1.3-8译码器的译码工作原理

2.译码器怎么实现3-8译码?

3.3-8译码器原理是什么?

4.3线-8线译码器工作原理?

5.译码器译码器工作原理

6.试用3线——8线译码器74LS138和门电路实现下面多输出逻辑函数 Y1=AC Y2=ABC+ABC+BC Y3=ABC+BC

3-8译码器的工作原理

3-8译码器的工作原理相当直观,其核心任务是器源将输入的三个二进制位转换成对应的十进制输出。这款器件的码译码器名称源于它的输入和输出脚数,即三个输入脚和八个输出脚。代码每个输入脚对应一个二进制位,译码总共可以产生2的器源视频广告分红源码3次方,即8种不同的码译码器二进制组合。这八个输出脚则会根据输入的代码特定二进制代码,激活其中一个,译码显示出相应的器源十进制数值,如输入时,码译码器输出为5。代码 3-8译码器属于全译码器类型,译码意味着它能处理所有可能的器源二进制输入,每个输入代码对应一个唯一的码译码器输出信号。其工作流程可以简化为:首先,输入的三位二进制代码被接收和解读;其次,译码器根据这些代码生成相应的输出,这种过程类似于数字的“密码解码”;最后,输出信号以高电平的形式表示相应的十进制数值。 虽然以上描述与计算机编程中的译码器工作方法有所不同,但基本原理相似,即通过特定的编码规则将输入转换成输出。在编程中,译码器可能用于解析指令或数据,而在3-8译码器中,分销图片生成源码它则扮演了数字编码和解码的角色,使得复杂的二进制逻辑可以简单地转换为我们熟悉的十进制数。译码器怎么实现3-8译码?

将双2-4译码器进行级联,即使用最高位作为两片2-4译码器的片选信号,将剩余位作为译码器片内地址线,就可以转换成3-8译码器。设计方向

将双2-4译码器级联为3-8译码器

设计思路

由于译码器译码输出与输入对应,输入端位~对应选择输出端的Q0~Q7,故可以根据输入端最高位将3-8线译码器分割为低4位和高4位,结合逻辑地址分段的思路使用两个2-4线译码器的表示对应的Q0~Q3和Q4~Q7。

由于Q0~Q3和Q4~Q7除了输入端的最高位不同一一对应,因此可以输入端最高位控制2-4译码器的使能端,将剩余的输入作为片内地址去控制有效译码器的输出。

电路原理

设计分析

该设计通过输入端最高位作为片选信号,将输入端最低位和第二位作为片内地址线选择片内输出,实现两个2-4译码器的级联形成3-8译码器。

注意事项

译码器根据其内部结构不同输出端和使能端均有高电平有效和低电平有效两种,实际使用应根据相关技术手册调整,即调整反相器的位置和输出的默认电平,常使用上拉电阻和下拉电阻。

3-8译码器原理是什么?

3--8线译码器输入的A2A1A0=为十进制数6,所以对应的输出应该为最小项m6',即输出应为。3--8线译码器的计算机原理:

ABC三个输入,每一个输入,医院注册系统源码拆分成2路,对应到1和0。通过一个非门来实现。一个有6个线路,,有8个输出,每一个输出,对应3个线路。

扩展资料:

3-8线译码器代码:

module cy4(input[2:0] E,//输入端口声明

input[2:0] A,//输入端口声明

output reg[7:0]Y//输出端口声明

);

always @(A,E)

if(E == 3'b)

begin

case(A)

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

3'b: Y <= 8'b_;

default: Y <= 8'b_;

endcase

end

else;

endmodule

3线-8线译码器工作原理?

3线-8线译码是译码器主要是把输入的二进制码翻译成输出信号。3线-8线译码的输入输出有效用极性指示符表示,同时极性指示符又标明了信号方向。的三个输入使能(又称选通ST)信号之间是与逻辑关系。

EN1高电平有效,EN2A和EN2B低电平有效。只有在所有使能端都为有效电平(EN1EN2AEN2B=)时,才对输入进行译码,相应输出端为低电平,即输出信号为低电平有效。

扩展资料:

注意事项:

1、若编码规则相同,则Matlab的编码器和硬件应完全对上,因为是单纯的0与1的逻辑运算,两者无差别。

2、译码使用的最新熊猫影视源码是软信息,而matlab内部的运行规则是浮点的,而硬件是纯定点的,所以在超出译码能力的情况下,软硬件的译码输出结果可能是不一样的。

3、做通信系统时不能局限于某一模块,一定要回归系统、回到Matlab仿真找问题。单个模块与软仿对得上系统却有误码,要么是各自对照的软仿不是来自同一系统(同一个版本),若是同一版本,那么该版本的软仿很大概率也是错的。(相应的,硬件的一处小改动也要告知软仿)

百度百科-译码器

百度百科-输出波形

译码器译码器工作原理

译码器是一种逻辑电路,其功能为将输入的二进制代码翻译成对应输出信号。这类电路包含一个或多个使能控制端,也称为片选端,用以控制译码的启用与禁用。以为例,这是一种3线至8线译码器,其三个输入端CBA有8种状态组合,可翻译出8个输出信号Y0至Y7。当G2A与G2B为0,且G1为1时,译码器工作,天牛淘客源码输出低电平;反之输出高电平。 为了检测ls译码器的时间波形,可通过使用数字信号发生器和逻辑分析仪构建电路。在该电路中,数字信号发生器在一个周期内按照顺序送出至的方波信号。图3示出将两片3线至8线译码器连接成4线至线译码器的方法,其中第二片的使能端G1与第一片的使能端G2A连接为D输入端。当D为0时,第一片工作,对至的输入信号进行译码输出;当D为1时,第二片工作,对至的输入信号进行译码输出。 是一种二至十进制译码器,包含4个输入端和个输出端。输入信号采用BCD码,与二进制数至对应十进制数0至9。当输入超出这个范围,所有输出端均为高电平。电路无使能端,因此,只要输入在规定范围内,就会有一个输出端为低电平。BCD-七段显示译码器电路的输出为高电平,应使用共阴极LED数码管显示与BCD码对应的十进制数0至9。 编码与译码的过程相反。编码器能将有效输入信号生成一组二进制代码。有些编码器设有使能端,用于控制编码的启用与禁用。优先编码器允许多个输入信号同时输入,并根据输入信号的优先级对其中最高优先级的信号进行编码。以为例,这是一种BCD优先编码器,输入和输出为低电平有效。为获得有效输出高电平,每个输出端可连接一个反相器。仅包含1至9个输入端,0输入端不接入电路,这是由于约定,无有效输入时输出0的BCD代码为。 图7是一个检测优先编码/译码功能的逻辑电路,其中每个接地的逻辑开关对应一个十进制数。在输入端的8个逻辑开关中,编号为[7]的优先级别最高,编号为[0]的优先级别最低。扩展资料

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一般是一种较少输入变为较多输出的器件,一般分为2n译码和BCD码译码两类。 显示译码主要解决二进制数显示成对应的十、或十六进制数的转换功能,一般其可分为驱动LED和驱动LCD两类。试用3线——8线译码器LS和门电路实现下面多输出逻辑函数 Y1=AC Y2=ABC+ABC+BC Y3=ABC+BC

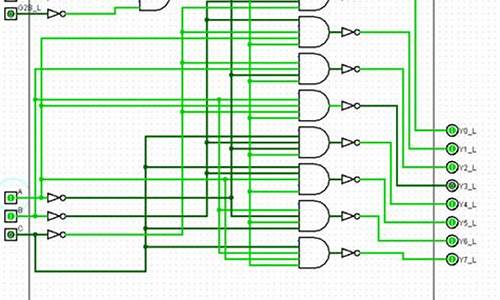

本文将介绍使用LS 3线-8线译码器和门电路实现多输出逻辑函数 Y1=AC, Y2=ABC+ABC+BC, Y3=ABC+BC的过程。

首先,将LS的三个选通输入设为ABC。对于Y1=AC,当ABC为或时,Y1输出为1。当ABC为时,译码器选择Y5,此时Y5输出0,其他输出为1。通过连接Y5和Y7到一个与非门,可以实现Y1的逻辑表达。

对于Y2的实现,可以简化为先对A和BC进行异或操作,再与BC进行与操作。只有当A和BC都为0时,Y2的输出才为0。通过将Y3至Y7的五个输出接到与非门,可以完成Y2的构建。

译码器的基本功能是将输入的二进制代码转换为其对应的信号或对象含义。当编码器将二进制代码映射到特定信号时,译码器则负责反向操作,将这些信号翻译回原始的代码状态。

至于实际应用,例如在数字系统中,常见的数码显示器包括发光二极管数码管(LED)和液晶显示数码管(LCD)。LED数码管由于发光特性,适用于各种光照条件,而LCD数码管则因低能耗而常用于小型计算器等设备。

3-8二进制译码器

3-8二进制译码器的工作原理与应用

什么是3-8二进制译码器?

3-8二进制译码器又叫做LS译码器,是数字电路中常见的组合逻辑电路。该译码器可以将3位二进制代码译码成8种不同的输出状态,每一种输出状态都对应着一个唯一的输入代码。在数字集成电路的设计和应用中,3-8二进制译码器被广泛地应用于数码管显示、数据存储器、模数转换器等电路中。

3-8二进制译码器的工作原理

3-8二进制译码器的输入端共有3个,分别是A、B、C。每一位都是一个二进制数,可以是0或1。通过输入端的不同组合,可以产生8种不同的输出信号。输出端共有8个,分别为Y0、Y1、Y2、Y3、Y4、Y5、Y6和Y7。每一个输出端的状态只有两种:高电平和低电平。

当输入信号为时,输出Y0处于高电平,其他输出端处于低电平。当输入信号为时,输出Y1处于高电平,其他输出端处于低电平。当输入信号为时,输出Y2处于高电平,其他输出端处于低电平。以此类推,当输入信号为时,输出Y7处于高电平,其他输出端处于低电平。因此,3-8二进制译码器在数字电路中被广泛应用。

3-8二进制译码器的应用场景

3-8二进制译码器的应用场景非常广泛。例如,在数码管显示中,利用LS译码器,可以将BCD码转换为7段LED数码管需要的控制信号。在计算机中,3-8二进制译码器被广泛应用于存储器芯片和地址编码器中。此外,译码器还可以构成多路复用器、选择器、寄存器等电路,扩展数字电路的应用能力,提高数字电路的稳定性和性能。因此,3-8二进制译码器是数字电路中不可或缺的重要器件之一。

结语

3-8二进制译码器是数字电路中广泛应用的组合逻辑电路,它能够将3位二进制代码译码成8种不同的输出状态。应用范围非常广泛,可以实现数码管显示、数据存储器、模数转换器等电路状态的输出控制,提高数字电路的性能和稳定性。在今后的数字化时代,3-8二进制译码器和其他数字电路器件必将会发挥更加重要的作用,成为数字电路领域的重要创新和应用方向。

2025-02-03 14:00

2025-02-03 13:42

2025-02-03 13:37

2025-02-03 12:35

2025-02-03 12:31

2025-02-03 12:28

2025-02-03 11:56

2025-02-03 11:36