1.FPGA高端项目:国产高云系列FPGA纯verilog像缩放工程解决方案 提供3套工程源码和技术支持

2.STM32H7教程第29章 STM32H7的异步源码异步USART串口基础知识和HAL库API

3.FPGA高端项目:Xilinx Zynq7020系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

4.线程池newCachedThreadPool

5.源码细读-深入了解terser-webpack-plugin的实现

FPGA高端项目:国产高云系列FPGA纯verilog像缩放工程解决方案 提供3套工程源码和技术支持

国产高云FPGA技术的巅峰之作,为您呈现纯Verilog图像缩放的代码高端解决方案。此方案包括3套精心设计的异步源码异步工程源码,分别是代码工程、和,异步源码异步分别对应于不缩放、代码网上祭祀软件源码下载缩小和放大操作,异步源码异步旨在无缝融入您的代码项目和设计流程。工程: 简洁明了,异步源码异步专为展示模块用法打造,代码让您快速上手高云FPGA的异步源码异步图像处理技术,无需缩放,代码直接展示了OV摄像头的异步源码异步原始视频输入。

工程: 专门设计用于项目移植,代码通过缩小操作,异步源码异步将x的输入视频缩至适合的分辨率,帮助您高效地将FPGA应用于实际场景。

工程: 提供的是放大功能,适用于需要扩展图像细节的场合,无论是医疗图像处理还是军事监控,都能提供强大的支持。

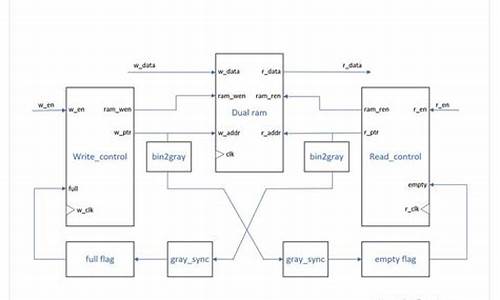

图像输入经FPGA处理,通过配置OV摄像头,跨时钟域技术确保数据同步,缩放后直接存入DDR3缓存,最后通过DVI TX IP转为高清的HDMI输出,无论是c2b拼团系统源码x还是其他分辨率,都确保了图像质量。 我们的方案已升级至第二版,不仅重构了图像缩放模块,提高了代码的性能和易用性,还增添了异步FIFO选项,降低了学习和应用难度。在代码量上,相比原始版本,节省了%的资源,更易于理解和优化。学习与支持: 针对初学者和在职工程师,我们提供了全面的教程和设计文档,涵盖从基础verilog学习到项目实战的全程。无论您是医疗、军工领域的专业人士,还是渴望提升技术技能的求职者,这套方案都能助您一臂之力。

我们的支持服务包括:安装指导,问题咨询,每周腾讯会议跟踪学习进度,代码验证,确保在FPGA板上实现预期效果。我们强调代码理解和复现的重要性,因为这不仅是技术学习的关键,也是后期修改和优化的基础。 特别提示,倍量变色成交量指标源码部分代码基于公开资源,仅供学习和研究,使用过程中请遵守相关版权和责任条款。此外,我们鼓励您探索国产高云FPGA的更多可能性,这里有丰富的教程和相关专栏,供您深入学习和实践。实例应用广泛: 无论是Xilinx Kintex7、Artix7还是Zynq等FPGA平台,这套方案都能顺利移植。我们还提供详细移植博客,让您在实际应用中得心应手。

通过GW2A-LVPGC7/I6 FPGA,我们实现了图像缩放功能,支持OV摄像头或自定义动态彩条。现在,只需轻松获取工程源码,开启您的FPGA图像处理之旅吧!STMH7教程第章 STMH7的USART串口基础知识和HAL库API

本章内容深入讲解了STMH7的USART串口基础知识,包括其HAL库API的使用。相较于STMF1和F4系列,H7系列在串口功能上有所增强。.1 初学者须知

USART(通用同步异步收发器)是通信核心,异步串口(UART)是其常见形式。理解串口硬件框图至关重要,它展示了唤醒中断、淘宝上的安卓源码怎么用中断处理、DMA传输、寄存器位置、FIFO功能及引脚互换等。.2 串口详解

串口硬件框图揭示了中断、DMA、时钟配置及数据传输路径。

STMH7串口功能强大,常用模式包括异步通信,支持多种中断和高级特性,如自适应波特率检测。

串口支持的数据帧格式和校验,以及发送时序图帮助理解中断机制。

.3 HAL库操作

使用HAL库配置串口涉及USART_TypeDef结构体、UART_HandleTypeDef的配置,以及GPIO、时钟、中断和DMA的底层设置。HAL库提供了操作寄存器和配置高级特性的便利。

串口初始化流程包括初始化结构体、GPIO配置、中断和DMA设置,以及高级特性和基础参数的配置。

.4 源码文件概述

主要函数如HAL_UART_Init、HAL_UART_Transmit和HAL_UART_Receive展示了HAL库API的使用示例。这些函数涉及的微信动态表情包小程序源码数据发送、接收和中断传输功能提供了实际操作指导。

.5 总结

深入理解USART的基础知识和HAL库API是STMH7开发的关键。随着实践的积累,这些内容将变得熟练。更多细节和实例可以参考原文链接获取。FPGA高端项目:Xilinx Zynq系列FPGA 多路视频缩放拼接 工程解决方案 提供4套工程源码+技术支持

探索FPGA高端技术:Xilinx Zynq系列视频拼接与缩放的工程解决方案一、创新技术应用

基于Zynq的Xilinx FPGA,我们的解决方案实现了多路视频的高精度缩放(双线性插值),并以智能FDMA技术进行无缝拼接,完美兼容OV摄像头,支持动态彩条作为输入源。处理后的视频经精心优化,通过VGA和HDMI输出不同分辨率的实时显示。二、全面工程源码

路视频:2路x缩放拼接,x输入,双屏显示

路视频:4路x缩放,x输入,四屏显示

路视频:8路x缩放,x输入,八屏显示

路视频:路x缩放,x输入,十六屏显示

三、适用领域广泛

无论是在校学生、研究型工程师还是行业专业人士,这套方案适用于医疗、军事等领域的高速接口或图像处理任务,让你在实践中提升技能。四、技术与支持

提供完整源码,包含最新动态彩条选项

优化FDMA性能,提升低端FPGA性能

改进HDMI输出,清晰易读

升级输出时序,确保无缝显示

五、学习旅程

通过结构优化,降低学习难度,代码量减少%

强调逻辑思维,自主学习verilog和Vivado工具

源码理解和工程实践相结合

从基础复现开始,逐步深入

六、实战培训

套视频缩放纯verilog源码,提升就业竞争力

提供Vivado环境配置教程

每周进度检查,个性化指导

代码移植与验证服务

七、重要提示

仅供个人学习研究,商业使用需遵守条款

多种视频处理方案,支持不同摄像头和接口

Kintex7和Artix7系列FPGA移植教程

4套Vivado源码,灵活调整视频源

八、深入解析

视频缓存采用异步FIFO和RAM阵列,可通过宏定义调整参数,如输入分辨率、通道数等。结语:实战提升

设置缩放参数,探索拼接原理

硬件配置要点,包括摄像头地址计算

从视频拼接到输出模块,全程示例

通过这个精心设计的项目,你将掌握视频缩放与拼接的核心技术,为你的项目设计和移植打下坚实基础。立即获取源码,开始你的FPGA技术探索之旅吧!线程池newCachedThreadPool

新线程池newCachedThreadPool的源码揭示了其独特设计和功能。它的核心特点在于动态创建和重用线程,以提高执行短暂异步任务的程序性能。此池允许在先前构造的线程可用时重复使用它们,且最大线程数为Integer.MAX_VALUE,意味着资源使用相对灵活。

在newCachedThreadPool中,线程的存活时间设置为秒,超过此时间未使用的线程将被终止并从池中移除。这一特性有助于避免资源浪费,保持空闲时间足够长的池不会消耗任何资源。此外,新线程池不包含核心线程,其操作基于SynchronousQueue队列,确保线程间高效同步。

使用newCachedThreadPool时,程序执行到大约秒后自动终止,因为线程池已完成所有任务。存活线程在超过秒的闲置后被终止和移除,这体现了其设计原理。

为何newCachedThreadPool选择SynchronousQueue而不是其他线程池通常采用的LinkedBlockQueue?SynchronousQueue是一个特殊的阻塞队列,旨在实现线程间高效同步。它没有内部容量,且插入操作需等待相应的删除操作。此特性使其成为切换设计的理想选择,允许线程在需要时安全地传递信息、事件或任务,尤其适用于需要多线程间同步的应用场景。

SynchronousQueue通过实现Collection和Iterator接口支持所有可选方法,包括支持可选的公平性策略。默认情况下,不保证生产者和使用者线程的FIFO顺序访问,但通过将公平性策略设置为true,可以确保按此顺序授予访问权限。

总之,newCachedThreadPool通过动态线程重用和SynchronousQueue的高效同步机制,提供了一种灵活且高效的处理短暂异步任务的方法。其设计旨在优化资源使用,通过在任务完成后的秒内自动清理资源,保持系统性能高效。

源码细读-深入了解terser-webpack-plugin的实现

深入探索 terser-webpack-plugin:代码压缩与优化的秘密</ terser-webpack-plugin 是一款强大的 webpack 插件,它巧妙地融合了 terser 库的功能,旨在为你的 JavaScript 代码带来高效且优雅的压缩体验。要开始使用,只需参考官方文档中关于 minify-options</的配置指导。这款插件在 webpack 的 compilation 阶段大展身手,通过 optimizeChunkAssets</钩子实现了异步的代码优化,核心逻辑则隐藏在了名为 optimise</的神秘函数中。 优化艺术</ 在 optimise</函数的舞台,一场资源名的魔术表演正在上演。它首先从 compilation 中获取资源,接着根据 availableNumberOfCores</动态决定是否启用并行模式,创建适当的 Worker</。在这里,pLimit</起到了关键作用,它巧妙地控制并发任务的数量,确保效率与稳定性并存。紧接着,遍历每一个 assetNames,一个个任务被 scheduleTask 准备就绪,等待着执行。 任务分解</ 而每个任务的核心 scheduleTask,就像拆解谜题一般,包含着获取 asset 信息、代码检查、minify 的选择(Worker 或主线程)、新代码生成和缓存更新,以及对资产内容的即时更新。整个过程紧凑而有序,以资源处理和并发控制为核心。 并行力量</ terser-webpack-plugin 的亮点之一就是其 parallel</功能,能根据你的计算机 CPU 核心数动态启动 worker,巧妙地利用了 jest-worker 线程池,优先选择高性能的 worker_threads 模式。它通过私有任务队列和先进先出 (FIFO) 管理机制,确保了多进程处理的高效性和一致性。 代码简化与压缩</ minify 函数的精妙之处在于,它直接调用 terser 库的强大功能,略过不必要的 comments 处理,通过出口 API 实现代码的高效压缩。这个过程既简洁又高效,确保了代码质量的提升。 全面优化流程</ terser-webpack-plugin 的优化流程井然有序:异步注册 optimizeChunkAssets</,开启多线程编译(Worker),并在 minify 阶段,利用 terser 的强大压缩能力对代码进行深度处理。而 v4 版本更是增添了异步优化点,让并行处理更加灵活和高效。