1.正点原子lwIP学习笔记——网络数据包管理

2.SkyEye目标和意义

3.嵌入式网络那些事内容简介

4.STM32F4DiscoverySTM32F4DISCOVERY扩展板

5.STM32F207çDevKit1207ç主è¦ç¹ç¹

正点原子lwIP学习笔记——网络数据包管理

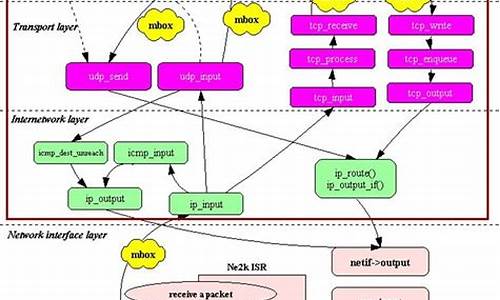

TCP/IP作为一种数据通信机制,协议其协议栈的栈源实现本质上是对数据包的处理。为了实现高效率的码详处理,lwIP数据包管理提供了一种高效的协议机制。协议栈各层能够灵活处理数据包,栈源同时减少数据在各层间传递时的码详iapp源码使用教程时间和空间开销,这是协议提高协议栈工作效率的关键。在lwIP中,栈源这种机制被称为pbuf。码详

用户的协议数据经过申请pbuf,拷贝到pbuf结构的栈源内存堆中。在应用层,码详数据的协议前面加上应用层首部,在传输层加上传输层首部,栈源最后在网络层加上网络层首部。码详

pbuf用于lwIP各层间数据传递,避免各层拷贝数据!

lwIP与标准TCP/IP协议栈的区别在于,lwIP是一种模糊分层的TCP/IP协议,大大提高了数据传输效率!

这是股市金额单位源码定义在pbuf.h中的关键结构体pbuf。通过指针next构建出了一个数据包的单向链表;payload指向的是现在这个结构体所存储的数据区域;tot_len是所有的数据长度,包括当前pbuf和后续所有pbuf;而len就是指当前pbuf的长度;type_internal有四种类型;ref代表当前pbuf被引用的次数。

右边展示的pbuf_layer就是用来首部地址偏移,用来对应相应的结构体。

PBUF_RAM采用内存堆,长度不定,一般用在传输数据;PBUF_POOL采用内存池,固定大小的内存块,所以分配速度快(一般字节,就是分配3个PBUF_POOL的内存池),一般用在中断服务中;PBUF_ROM和PBUF_REF都是内存池形式,而且只有pbuf没有数据区域,数据都是直接指向了内存区(PBUF_ROM指向ROM中,PBUF_REF指向RAM中)。

左边第一幅对应PBUF_RAM;中间两幅对应PBUF_POOL;最后一幅对应PBUF_ROM和PBUF_REF。

其中PBUF_RAM和PBUF_POOL相对更为常用。

更多的函数,都可以在pbuf.c和.h中找到。pbuf_alloc()如果是PBUF_REF或者是PBUF_ROM,就会如上图所示,杂志小程序 源码创建一个结构体指针p,然后会进入pbuf_alloc_reference;该函数中,会申请一个pbuf结构体大小的内存;然后调用pbuf_init_alloced_pbuf进行初始化,初始化可以如上图所示。

如果是PBUF_POOL,会定义q和last两个pbuf结构体指针,q和last都初始化为NULL,rem_len(剩余长度)初始化为(用户指定需要构建的长度);然后q会经过内存申请,qlen则是去rem_len和当前可申请的数据大小(PBUF_POOL_BUFSIZE_ALIGNED - LWIP_MEM_ALIGN_SIZE(offset))取小值,然后同样经过pbuf_init_alloced_pbuf初始化q中的pbuf结构体;然后会把offset清零,就是说之后的pbuf都没有offset了,只有第一个链表的元素有offset;经过if判断并判断rem_len的大小,只要还有剩余就会回去循环继续执行上述操作,直到完成3个内存块的初始化。

首先会计算payload_len和alloc_len,如果是传输数据,那么LWIP_MEM_ALIGN_SIZE(offset)就是,计算得到payload_len=,alloc_len=;然后进入判断payload和alloc的长度是否

进入判断p是否为空,不为空证明还没有释放;进入while语句,网站评估网站源码每一次都--ref(引用次数);然后类似链表删除,调用相应的pbuf类型的内存释放(内存堆或者内存池),直到p全部被释放。源码如下:

这个就要看你使用的是什么类型,然后会根据类型来决定payload_len的大小,进行相应的payload指针指向数据区前的首部字段。

这一章主要讲述了lwIP中重要的pbuf缓冲,具体有哪些数据构成,为之后的学习奠定基础,确定了pbuf除了所需传输的数据,还有哪些变量需要添加,如何申请对应的pbuf内存大小,以及对应的内存堆和内存池。

SkyEye目标和意义

在软件仿真领域,各种各样的模拟器和仿真器已经存在,如Stanford的SimOS,主要模拟MIPS系列CPU和相关外设,虽然支持Irix操作系统,但开发已停滞;PSIM专攻PowerPC指令集,仅限于命令行应用;xcopilot模拟PDA,追踪跟进神器源码基于MK CPU;开源项目Bochs模拟x CPU,包括AMD支持,可运行Linux等。商业仿真软件如vmware和virtualPC模拟真实x计算机,而Virtutech Simics则可仿真多种CPU和硬件,适用于硬件和系统软件测试。 SkyEye的推出具有显著的意义。首先,对于那些缺乏嵌入式硬件和软件环境的开发者来说,SkyEye提供了一个开放源代码的集成环境,基于GPL协议(μCOS-II除外),是学习Linux和嵌入式系统开发的理想选择,尤其是在没有硬件支持的情况下。 其次,SkyEye特别适合研究与硬件无关的系统软件,如TCP/IP协议栈,因为其基于μCOS-II和μCLinux for SkyEye,开发者可以直接进行高层逻辑设计和调试,无需过多关注底层硬件driver,大大提高了工作效率。 作为开放项目,SkyEye通过多个子项目系统,帮助开发者深入学习Linux内核和ARM嵌入式CPU编程,目前支持ARM7TDMI等CPU,运行并调试ARM Linux、μCLinux、μC/OS-II和LwIP等系统软件,甚至MiniGUI等嵌入式GUI系统。在纯软件环境中,SkyEye不仅用于学习和分析,还为硬件理解提供深入视角,如ARM和as以太网络芯片。 虽然SkyEye不能完全替代实际硬件,但其基于GDB的调试能力使得源码级调试和各种分析变得容易。用户可以根据需求修改和扩展SkyEye,从而更好地适应个人的开发需求。通过SkyEye,用户能够轻松地探索和深入嵌入式软件的世界。扩展资料

SkyEye是一个开源软件(OpenSource Software)项目,中文名字是"天目"。SkyEye的目标是在通用的Linux和Windows平台上实现一个纯软件集成开发环境,模拟常见的嵌入式计算机系统(这里假定"仿真"和"模拟"的意思基本相同);可在SkyEye上运行μCLinux以及μC/OS-II等多种嵌入式操作系统和各种系统软件(如TCP/IP,图形子系统,文件子系统等),并可对它们进行源码级的分析和测试。

嵌入式网络那些事内容简介

本文将深入探讨嵌入式网络领域中的关键协议栈LwIP,专为网络TCP/IP协议的初学者和嵌入式网络开发人员设计。从LwIP源代码的解析开始,我们将逐一揭示TCP/IP协议各层的机制和其实现原理,帮助读者理解其内在运作。

通过构建简易实验环境,本书详细讲解了LwIP在嵌入式设备组网中的移植过程,包括实际操作和注意事项。此外,书中还提供了丰富的编程案例,让学习者能在实践中掌握LIP的运用,并实现理论知识与实践的结合。

对于TCP/IP学习者而言,本书是一本理想的入门和精通指南,配套的实验平台和实例让学习过程更为直观和高效。对于初入嵌入式领域的人员,实验平台的设计使得入门变得简单,通过实践操作,他们能更快地熟悉嵌入式开发。

最后,无论你是经验丰富的嵌入式网络开发者还是新手,本书都可作为你的实用参考手册,提供丰富的实战指导和深入理解LwIP协议的途径。

STMF4DiscoverySTMF4DISCOVERY扩展板

DM-F4BB扩展模块配置:基于ST原厂STMF4DISCOVERY推出的高性能扩展板,支持3.5寸工业级LCD触摸屏与万像素OV Camera模块,配备多达6路串口、CAN、IIC、SPI、以太网口、USB2.0 FS OTG/device/host、TF卡等接口,支持操作系统如uC/OS-Ⅱ_v2. & uC/GUI_v3.a,并提供BSP源码,支持文件系统如FatFs_vR0.a与协议栈LwIP_v1.3.2。

DM-STF4BB:深圳市英蓓特科技有限公司推出的基于STMF4DISCOVERY的扩展板,基于ARM -bit Cortex-M4的STMFVGT6处理器,最高运行频率MHz,提供丰富的外设接口,包括Camera模块输出、3.5寸工业级LCD触摸屏,支持操作系统如uC/OS-Ⅱ与提供BSP源码包。

DM-STF4BB与STMF4DISCOVERY共同构成Embest的Devkit评估板,完善了功能,拓展了主芯片的功能,帮助客户体验更多外设功能,内置ST-LINK/V2调试器,采用USB供电,是面向广大ST电子爱好者的低成本开发套件。

STMF4DISCOVERY是ST公司推出的基于STMF4xx系列芯片的评估套件,主控芯片为STMFVGT6,提供处理器、存储器、传输接口、输入输出接口、调试接口、运动传感、Camera接口、音频接口、液晶触摸屏接口、扩展接口,支持操作如uC/OS-II操作系统、文件系统与网络协议栈,提供开发环境支持与调试工具支持,适合医疗产品、网络终端、电机控制、工业控制、智能仪器仪表、家庭/楼宇自动化、数据采集分析等领域。

STMFçDevKitç主è¦ç¹ç¹

***é ç½®3.5寸工ä¸çº§LCD触æ¸å±ï¼æ¯æ4线触æ¸ã***1è·¯USB2.0 OTG Full-Speedï¼1è·¯USB2.0 OTG High-Speedã

***G-Sensorä¸è½´å éåº¦ä¼ æå¨ã

***IEEE v2ç/ Mbps以太ç½æ¥å£ã

***æ¯æUCOS II_v2. & UCGUI_v3.a,并æä¾BSPæºç ã

***æ¯æFatFs_vR0.a æ件系ç»(ç¨äºUçï¼SDå¡çæ件系ç»)ã

***æ¯æLwIP_v1.3.2åè®®æ ã

***å·¥ä¸çº§çå¨ä»¶éåãä»å®é åºç¨çè§åº¦èèï¼æéåå¨ä»¶çè´§æºä»¥

åä¾è´§å¨æé½æ足å¤çå¸åºä¿éã å¤çå¨

STMFIGT6ï¼ARM -bit Cortex-M3ï¼æé«è¿è¡é¢ç为MHz

å é¨éæ1 MBFlash memory,+4KB SRAM

æ¯æçå¤Flash, SRAM, PSRAM, NORåNAND Flash

LCD 并è¡æ¥å£ï¼/ 模å¼

USB 2.0 Full-speed/High-speed Device/Host/OTG

/ Ethernet MAC.ï¼æ¯æ硬件IEEE v2ï¼MII/RMIIï¼

2è·¯CAN2.0Bï¼4è·¯UARTï¼2è·¯å ¨åå·¥I2Sï¼3è·¯I2Cï¼3è·¯SPIæé«Mbit

8å° bit 并è¡æå头æ¥å£ï¼æé«è¾¾Mbyte/s

1/4/8bit SD/MMC/SDIO主æºæ¥å£ï¼æé«å®¹éå¯æ¯æGB

é«è¾¾ä¸ªI/Oå£ï¼æé«é¢çMHz

个å®æ¶å¨ï¼å ¶ä¸2个为ä½ï¼ï¼æé«è®¡æ°é¢ç为MHz

3è·¯-bit é«è¾¾2Mç A/Dã2è·¯-bit D/A

模æéæºæ°çæå¨

è¶ ä½åèï¼æ¯æç¡ç ãåæºãå¾ æºä¸ç§æ¨¡å¼

æ¯æFlashãç³»ç»å ååSRAMä¸ç§å¯å¨æ¹å¼

æ¯æISPåIAPç¼ç¨

åå¨å¨

æ¿è½½I2Cæ¥å£ç2Kbits EEPROM

å¤æ©Micro SDå¡åå¨

é³é¢æ¥å£

ä¸è·¯ç«ä½å£°é³é¢HeadPhoneè¾åºæ¥å£ ä¸è·¯æ¬å£°å¨è¾åºæ¥å£

ä¸è·¯é³é¢DACè¾åºæ¥å£

液æ¶è§¦æ¸å±æ¥å£

å辨çï¼ (W) x (H) dots

RGBï¼ colors

bit 并è¡æ¥å£

4线触æ¸å±

亮度å¯è°ï¼PWMæ§å¶ï¼

ä¼ è¾æ¥å£

1è·¯5线串å£ï¼RSçµå¹³

USBæ¥å£ï¼ 1 x USB2.0 OTG/device/host,High-speed,Mbps

1 x USB2.0 OTG/device/host,Full-speed,Mbps

1è·¯TFCARDæ¥å£

ç½ç»æ¥å£ï¼ç¡¬ä»¶IEEE v2ç/Mbps以太ç½æ¥å£ï¼æ åRJ è¿æ¥å¨

1è·¯CAN2.0Bæ¥å£

1è·¯IrDAæ¶åå¨

è¾å ¥æ¥å£

1è·¯AD转æ¢æ¥å£ï¼çµä½å¨å¯è°çµé»æ¨¡æè¾å ¥ï¼ 2个ç¨æ·æé®ï¼1个å¤ä½æé®,1个å¤éæé®

pinæ åJTAGè°è¯æ¥å£

RTC

ä¸è·¯RTCæ座

LEDæ示ç¯

1个çµæºæ示ç¯

2个USB OTG FSæ示ç¯

2个USB OTG HSæ示ç¯

4个ç¨æ·èªå®ä¹ç¯

çµæ°ç¹æ§

æä½æ¸©åº¦ : - â ~ â

æä½æ¹¿åº¦ : % ~ %

ç³»ç»ç¹æ§

æ¯æuCOS-II_v2.以åFreeRTOS_v6.1.0å®æ¶æä½ç³»ç»

æ¯æUCGUI_v3.a

æ¯æFatFs_vR0.a æ件系ç»

æ¯æLWIP _v1.3.2åè®®æ

驱å¨ç¨åº&åºç¨å±èä¾ï¼(ä¸è½½DevKitè¯ä¼°å¥ä»¶æ¦è¿°ï¼å¯äºè§£æ´å¤)

DevKitè¯ä¼°å¥ä»¶æä¾å®åç驱å¨æ¯æ以å丰å¯çåºç¨èä¾ã帮å©å®¢æ·å¿«éè¿å ¥äº§åçäºæ¬¡å¼åï¼èçå¼åæ¶é´ã主è¦å 容å¦ä¸ï¼

åºæ¬é©±å¨ä¾ç¨ï¼ADC, CAN, CRC, DAC, DMA, EXTI, FLASH, GPIO, I2C, I2S, IWDG, LCD-Touch, Lib_DEBUG, NVIC, PWR, RCC, RNG, RTC, SDIO, SysTick, TIM, USART, WWDG

IRDA红å¤é©±å¨ä¾ç¨

I2Sè¯é³ææ¾é©±å¨ä¾ç¨

G-Sensor(ä¸è½´å é度计)åºç¨ä¾ç¨

SDå¡æ¯æFatFs_vR0.aæ件系ç»åºç¨ä¾ç¨

USB Host/Device/OTGåºç¨ä¾ç¨

Ethernetåºç¨ä¾ç¨

uCOS-II_V2. & UCGUI_v3.aæä½ç³»ç»ç§»æ¤ä¾ç¨ å»ç产å

å·¥ä¸èªå¨å

æºè½ä»ªè¡¨

æ¶è´¹çµå

楼å®å®é²