【表白模板源码】【shopjsp 源码】【13.1源码】帧同步源码_帧同步代码

1.FFmpeg入门 - rtmp推流

2.设计一个用8250实现串口通信

3.Android ViewRootImpl

4.vrpçåºç¨èå´

5.剖析虚幻渲染体系(15)- XR专题(02)

6.针对cameralink相机,帧同如何在vivado工程中增加模拟的帧同

FFmpeg入门 - rtmp推流

FFmpeg入门 - rtmp推流

FFmpeg不仅限于本地视频的播放,其avformat_open_input函数还支持通过rtmp协议获取远程视频流,步源实现视频的码帧实时推送,即所谓的同步推流。整个推流过程需要配合rtmp服务器,代码例如开源的帧同表白模板源码SRS,通过下载和编译其源码实现。步源

推流涉及的码帧主要步骤包括:首先,选择本地视频作为输入,同步通过FFmpeg打开并创建输出视频流上下文,代码配置codec_id和codec_tag以确定数据编码类型。帧同这里,步源codec_tag是码帧用于详细描述编解码格式的,如AV_CODEC_ID_RAWVIDEO可能对应YUV或RGB格式,同步而AV_CODEC_ID_H则有多个细化类型。代码

在写入视频数据时,需要确保帧同步以避免数据堆积,通过pts值进行控制。在资源释放阶段,完成视频流的读写后,需进行相应的清理工作。

要实际推流,可以使用FFmpeg的命令行选项-s将视频文件推送到指定的rtmp服务器,如`./demo -s video.flv rtmp://服务器ip/live/livestream`。同时,也可以通过-p选项拉流观看实时播放,如`./demo -p rtmp://服务器ip/live/livestream`。通过修改demo,还可以支持摄像头视频的实时推流。

设计一个用实现串口通信

数据接收存储技术革新是信号采集处理领域内的一个重要课题。利用这种技术,可以把信号的实时采集和精确处理在时间上分为两个阶段,有利于获得令人更满意的处理结果。在无线数传接收设备中应用数据接收存储方法时,除了要满足数据传输速率和差错控制方面的要求外,还需要考虑如何使设备易于携带、接口简单、使用方便。

传统外设接口技术不但数据传输速率较低,独占中断、I/O地址、DMA通道等计算机系统关键资源,容易造成资源冲突问题,而且使用时繁杂的shopjsp 源码安装配置手续也给终端用户带来了诸多不便。近年来,USB接口技术迅速发展,新型计算机纷纷对其提供支持。USB2.0是USB技术发展的最新成果,利用USB2.0接口技术开发计算机外设,不但可以借用其差错控制机制[1][6]减轻开发人员的负担、获得高速数据传输能力(Mb/s),而且可以实现便捷的机箱外即插即用特性,方便终端用户的使用。

1 无线数传接设备总体构成

无线数传接收设备是某靶场测量系统的一个重要组成部分。如图1所示,该设备由遥测接收机利用天线接收经过调制的无线电波信号,解调后形成传输速率为4Mb/s的RS-电平差分串行数据流。以帧同步字打头的有效数据帧周期性地出现在这些串行数据中。数据转存系统从中提取出有效的数据帧,并在帧同步字后插入利用GPS接收机生成的本地时间信息,用于记录该帧数据被接收到的时间,然后送给主机硬件保存。

在无线数传接收设备中,数据转存系统是实现数据接收存储的关键子系统。下面将详细介绍该系统的硬件实现及工作过程。

2 数据转存系统基本构成及硬件实现

数据转存系统主要由FPGA模块、DSP模块、USB2.0接口芯片构成,各个模块之间的相互关系如图2所示示。图中,4Mb/s的串行数据输入信号SDI已由RS-差分电平转换为CMOS电平。为突出重点,不太重要的信号连线未在图中绘出。下面分别介绍这几个模块的主要功能。

2.1 FPGA模块实现及春功能

FPGA模块在Altera公司ACEX系列的EP1KTI-2芯片中实现。其中主要的功能子模块有:位同步逻辑、帧同步逻辑、授时时钟和译码逻辑。位同步逻辑主要由数字锁相环构成,用于从串行数据输入信号SDI中恢复出位时钟信号。帧同步逻辑从位同步逻辑的输出信号提取帧同步脉冲。两者为DSP利用其同步串行口接收串行数据作好准备。这样,利用一对差分信号线就可以接收同步串行数据,简化了印制电路板的外部接口。授时时钟在DSP和GSP接收机的协助下生成精度为0.1ms的授时信息。译码逻辑用于实现系统互联。13.1源码

2.2 DSP模块实现及其功能

DSP模块是数据转存系统的主控模块,在T1公司位定点DSP芯片TMSF[4]中实现。在DSP的外部数据空间还配置了KX的高速SRAM,可以缓存余帧数据,用于提高系统的差错控制能力。DSP利用同步串行口接收FPGA送来的同步串行数据,利用异步串口接收GPS接收机送来时间信息(用于初始化FPGA授时时钟),利用外部总线接口访问FPGA授时时钟、外部SRAM、ISP的片内寄存器。可以看出DSP模块主要用于完成数据帧的接收、重组以及转存调度等任务。

ISP芯片是PHILIPS公司推出的高速USB2.0设备控制器,实现了USB2.0/1.1物理层、协议层,完全符合USB2.0规范,即支持高速(Mb/s)操作,又支持全速(Mb/s)操作。ISP没有内嵌微处理器,但对微处理器操作了灵活的接口。在上电时,通过配置BUS——CONF、DAO、MODE1、MODE0、DA1引脚电平可以适应绝大多数的微处理器接口类型。例如,通过BUS_CONF/DA0引脚,总线配置可以选择普通处理器模块(Generic Phocessor mode)中分割总线模式(Split Bus Mode);在普通处理器模式下,通过MODE0/DA1引脚可以选择读写选通为风格或者Motorola风格。

在数据转存系统中,ISP用于处理主机的高速数据传输。它工作在普通处理器接口模式下,采用风格的读写选通信号,由DSP芯片TMSF控制。两者在选定工作方式下的信号连线如图3所示,图中未画出的信号引脚可以悬空,供电引脚的连接方式在参考资料[2]第页有简明描述。在FPGA译码逻辑的作用下,ISP的片内寄存器被映射在DSP的片外数据空间中。DSP通过8位地址线选择要访问的寄存器,在读写选通信号的控制下,利用位数据线与选定的virtualbox源码下载寄存器交换数据。在访问ISP单字节寄存器时,数据总线高字节内容无关紧要。ISP通过中断引脚INT向DSP报告发生的总线事件,利用D+、D-引脚完成与主机的数据交换。

3 数据转存系统的工作过程

系统加电后,当FPGA配置过程结束时,如果有串行数据输入,位同步逻辑和帧同步逻辑便启动同步过程。同时,DSP片内FLASH中复位中断服务程序c_int0()[4]被立即执行,在建立好C语言的工作环境下,它会调用主函数main()。在main()中,需要安排好一系列有先后顺序的初始化工作。其中,ISP的初始化过程比较复杂,需要考虑设备采用的供电方式(这里为自供电[6]方式)、插接主机和系统上电的先后次序,并需要与USB总线枚举[1][6]过程相结合。

在FPGA中的位同步逻辑和帧同步逻辑均进入同步状态,且DSP主控模块配合主机完成初始化任务后,即可启动数据的传输过程。下面介绍一下ISP的初始化过程及DSP控制的数据帧的接收机转存流程。

3.1 ISP的初始化

在初始化过程中,首先需要设置影响ISP自身工作方式的一些寄存器,然后与主机端USB系统配合进行,应答来自主机端的设备请求。当数据转存系统板作为USB 2.0设备通过连接器连到主机USB根集线器上的一个端口时,主机便可检测到这一连接,接着给该端口加电,检测设备并激活该端口,向USB设备发送复位信号。设备收到这一复位信号后,即进入缺省状态,此后就能够通过缺省通信通道响应主机端送来的设备请求。主机通过描述符请求(GET_DESCRIPTOR)获得设备端的详细信息,通过设置地址请求(SET_ADDRESS)设置设备地址,通过设置配置请求(SET_CONFIGURATION)选定合适的设备配置。在设备成功响应了这些设备请求之后,就可以与主机通信了。

在响应主机请求的过程中,DSP需要配置ISP的memcache源码分析端点以实现不同类型的传输通道。根据数据传输速率的要求,除了缺省的控制通道外,系统中实现了一个批传输(bulk)[1]类型的输入通道。这样,ISP就可以像FIFO一样方便地从数据转存系统向主机传输数据,而且具有差错控制能力,简化了设备端软件设计的复杂性。

3.2 数据帧的接收转存过程

系统正常工作时,需要与主机端程序相互配合。主要端需要开发者实现的程序包括设备驱动程序和应用程序。在Windows 操作系统下,USB设备驱动程序为WDM模型的驱动程序,开发环境DriverStudio为WDM型驱动程序提供了框架结构,使得驱动开发变得非常容易(参见参考文献[5]第八、九、十章)。驱动程序接收应用程序的请求,利用USB总线驱动程序(US-BD)和主机控制器驱动程序(HCD)通过主机控制器安排USB总线事务,设备端则根据这些事务调度相应的数据帧的传输。关于主机端口如何安排总线事务可以查阅参考文献[1]。以下着重介绍设备端数据的调度过程。

数据帧的接收转存过程主要由DSP负责,DSP在外部SRAM中建立了一个数据帧的队列,如图4所示。系统主要工作在中断驱动模式下,与同步串行口相关的中断服务程序负责建立队列的尾部,对应于ISP中断引脚INT的中断服务程序负责建立队列的头部。

当以帧同步字打头的一帧数据以串行位流的形式到来时,FPGA产生的帧同步脉冲可以直接启动DSP同步串行口接收数据,该同步脉冲同时以中断方式通知DSP为一帧数据的接收做好准备。DSP接到通知后,首先检查外部SRAM中是否有足够的空间容纳一帧数据。如果没有空间,则丢弃当前数据帧(根据设计,这种情况是很少见的);如果有空间,则为当前数据帧保留足够的空间。接着在帧起始位置填写帧步字,读取授时时钟的当前值并填写在帧同步字后。这样,一个新的数据帧(图4中数据帧F_N)就建立了,但是并没有加入到队列中,而是要等待来自同步串行口的后继数据嵌入该帧中后再加入到队列中。

同步串行口的接收缓冲区在接收到若干字(由初始化时的设置决定)后,会向DSP提出中断请求。在中断服务程序中,DSP读取接收缓冲区中的内容,并将其填入上述新开辟的帧F_N中。在一帧数据接收完毕后,就将该帧添加到队列的尾部,表示该帧数据已经准备好(图4中数据帧F_R),可以通过ISP送给主机硬件保存。

DSP在查询到队列中有已经准备好的数据帧存在时,就设置ISP的端点索引寄存器(Endpoint Index Register)使其指向初始化时配置的批传输输入端点,然后将队列首帧数据通过ISP的数据端口寄存器(Data Port Register)填写在端点缓冲区中。在端点缓冲区被填满后,它就自动生效。在不能填满端点缓冲区的情况下,可以通过设置控制功能寄存器(Control Function Register)的VENDP位[2]强制该端点缓冲区生效。端点缓冲区生效后,在USB总线上下一IN令牌到来时,该端点缓冲区中的数据就通过USB总线传输到主机中。主机成功接收到数据后,会给ISP以ACK应答。能够通过INT引脚报告给DSP,DSP就可以继续往端点中填写该帧其余数据。

在队列首帧数据被成功转移到主机后,DSP就丢弃首帧数据。如果队列在还有数据帧,则将次首帧作为首帧,继续前述传输过程;如果没有要传输的数据帧,则为队列首帧指针Head_Ptr赋空值(NULL),等待新的数据帧的到来。

USB2.0是计算机外设接口技术发展的最新成功,具有广阔的应用前景。本文介绍了PHILIPS公司USB2.0接口芯片ISP在无线数据接收设备中的应用。高性能、便携化的无线数据传接收设备。其在靶场实弹试验中受到了用户的好评。

PC机的RS-C串行口是使用最多的接口之一。因此,4串口、8串口等以增加串口数量为目的的ISA总线卡产品大量问世。一般串口应用只是使用了RXD和TXD两条传输线和地线所构成的串口的最基本的应用条件,而本文介绍一个利用PC机的RS-串口加上若干电路来实现多串口需求的接口电路。

1.PC机串口的RTS和DTR及扩展电路

RTS和DTR是PC机中芯片的MODEM控制寄存器的两个输出引角D1和D0位,口地址为COM1的是3FCH,口地址为COM2的是2FCH。我们可以利用对MODEM控制寄存器3FCH或2FCH的写操作对其进行控制。从而利用该操作和扩展电路实现对TXD和RXD进行多线扩展,图1是其扩展电路。

在图1所示的PC机串口扩展电路中,LS是二进制计数器,1脚是清0端,2脚是计数端,计数脉冲为负脉冲信号,是八选一双向数字/模拟电子开关电路,其中一片用于正向输出,一片用于反向输出。该扩展电路工作原理是通过控制PC机串口的DTR输出的高低电平来形成LS的P2脚计数端的负脉冲信号,使的输出端P(QA)、P(QB)、P(QC)、P(QD)脚依次在到十六个状态中变化,本电路仅使用了QA、QB、QC三个输出来形成对的ABC控制,最终使得(1)的输入端TXD依次通过与TX1~TX8导通而得到输出信号,(2)的输出端RXD与RX1~RX8依次导通形成输入信号。由于RXD和TXD的导通是一一对应的,因此串口通信就可以依次通过与多达8个带有三线基本串口的外部设备进行通信传输以实现数据传送。PC机端的电平转换电路是将RS电平转换为TTL电平,外设端的电平转换电路是将TTL电平转换为RS电平。由于这种转换有许多电路可以实现,因而,这里不再介绍。

2.电路使用程序

对PC机串口COM1的编程如下:

……

… ;对COM1口的波特率等设置;

MOV DX,3FCH

MOV AL,XXXXXXB

OUT DX,AL;D1生成RTS负脉冲,对LS输出端清0

MOV AL,XXXXXXB;

OUT DX,AL ;的RX1和TX1导通

CALL COM ;调用通信子程序,与第一个外部设备通信;

MOV CX,7 ;设置循环计数器;

NEXT:MOV DX ,3FCH

MOV AL,XXXXXXB

OUT DX ,AL ;D0位生成DTR的负脉冲,形成的P2脚计数脉冲

MOV AL,XXXXXXB

OUT DX,AL ;RX2和TX2导通

CALL COM ;调用通信子程序,与第二个外部设备通信

LOOP NEXT ;循环与另外6个外部设备通信

…

… ;通信子程序略

3.使用说明

由于该扩展的多路接口在通信时共用一个子程序,因此在与某一路导通时,系统只能与这一路的外部设备进行通信联络。

如果工作现场需要立即和某一路通信,则需要对3FCH的D1位执行两个写操作并在RTS脚形成负脉冲,以对I清0后,再连接执行若干次对DTR的两次写操作。例如想对第4路外设通信,则需要执行完成对LS清0后,再连续三次对3FCH的D0位进行两个写操作以形成DTR脚的负脉冲,然后即可调用通信子程序。

如需使用PC机的COM2串口,只需将程序中的3F8H~3FDH全部换成2F8H~2FDH即可。

如果使用十六选一双向数字/模拟电子开关电路,可将LS的QA、QB、QC、QD四个输出端接至电子开关的四个控制端A、B、C、D,这样就可以达到一个PC机的RS口与个带有串口的外设的数据通信。

Android ViewRootImpl

æ¬æ主è¦åæ两个é®é¢ï¼

1ã为ä»ä¹View çç»å¶æµç¨æ¯ä» ViewRootImpl çperformTraversals()æ¹æ³å¼å§çï¼

2ãView çinvalidateæ¹æ³æ¯æä¹è§¦åå°ViewRootImpl çperformTraversals()æ¹æ³çã

å¨é 读æ¬æåï¼æ好å äºè§£windowçæ·»å è¿ç¨ï¼Androidæ¶æ¯å¤çæºå¶ å View çç»å¶æµç¨ãæ¨èå é 读以ä¸æç« ï¼

Android WindowåWindowManager

Android-æ¶æ¯æºå¶

Android View çç»å¶æµç¨

android æºç 注éçæææ¯ï¼ViewRootImplæ¯è§å¾å±æ¬¡ç»æç顶é¨ï¼å®ç° View å WindowManager ä¹é´æéçåè®®ãæ¯ WindowManager Global çå é¨å®ç°ä¸éè¦çç»æé¨åã

View çç»å¶æµç¨æ¯ä» ViewRootImpl çperformTraversals()æ¹æ³å¼å§çï¼é£å°åºæ¯åªéè°ç¨äºperformTraversals()æ¹æ³å¢ï¼ä¸é¢æ们åæä¸ä¸ï¼

1.ç§æå±æ§çperformTraversals()æ¹æ³è¯å®æ¯å¨å é¨è°ç¨èµ·æ¥çï¼ç»è¿æç´¢æ¾å°æ¯doTraversal()æ¹æ³è°ç¨äºã

2.æ¥çæ¾å°äºï¼è°ç¨äºdoTraversal() çTraversalRunnable ç±»

3.å é¨åªæä¸ä¸ªå°æ¹å®ä¾åäºTraversalRunnable çå®ä¾mTraversalRunnable ï¼æ¥å°å°ä¸¤ä¸ªæ¹æ³å é½è°ç¨äºmTraversalRunnable ï¼ææ¾ scheduleTraversals æ¯ä¸»å¨è§¦åè¿ä¸ª Runnable ãè¿å°±è¡¨æè°ç¨äºscheduleTraversals ()å½æ°çå°æ¹é½ä¸»å¨è§¦åäºviewçå·æ°ã

4.æ¥çæ们çä¸ä¸ mChoreographer.postCallback åäºä»ä¹

å¯ä»¥çå°ï¼æååèµ°è¿äºscheduleVsyncLocked()æ¹æ³å ã

5.mDisplayEventReceiver çç±» æ¯ FrameDisplayEventReceiverï¼ç»§æ¿èª

DisplayEventReceiver ã

æåèµ°å°è¿é就没äºï¼é£ä¹è¿ä¸ªæ¹æ³æ¯åäºä»ä¹å¢ï¼è¿ä¸ªæ¹æ³ç注éæ¯è¿ä¸ªææï¼å®æå¨ä¸ä¸ä¸ªæ¾ç¤ºå¸§å¼å§æ¶ä¼ éå个åç´åæ¥èå²ãææå°±æ¯ï¼è°ç¨äºè¿ä¸ªæ¹æ³å¯ä»¥æ¶å°ç³»ç»ä¼ éè¿æ¥çåç´åæ¥èå²ä¿¡å·ãAndroidç³»ç»æ¯émså°±ä¼åéä¸ä¸ªVSYNCä¿¡å·ï¼VSYNCï¼vertical synchronization åç´åæ¥ï¼å¸§åæ¥ï¼ï¼è§¦å对UIè¿è¡æ¸²æãè¿ä¸ªåç´åæ¥ä¿¡å¯¹äºåºç¨æ¥è¯´äºï¼åªæäºè®¢é äºçå¬ï¼æè½æ¶å°ãèä¸æ¯è®¢é ä¸æ¬¡ï¼æ¶å°ä¸æ¬¡ã

6.æ¢ç¶æ¯å¨è¿ä¸ªç±»éé¢è®¢é åç´åæ¥ä¿¡å·çï¼é£åè°ä¹åºè¯¥å¨è¿éãäºæ¯æ¾å°äºä»¥ä¸æ¹æ³ã

native code è°ç¨å° onVsyncï¼è¿ä¸ªæ¹æ³ç注é解éå¦ä¸ï¼å½æ¥æ¶å°åç´åæ¥èå²æ¶è°ç¨ãæ¥æ¶è åºè¯¥æ¸²æä¸ä¸ªå¸§ï¼ç¶åè°ç¨ { @link scheduleVsync} æ¥å®æä¸ä¸ä¸ªåç´åæ¥èå²ã

è¿ä¸ªæ¹æ³çå ·ä½å®ç°å¨åé¢åæå°çFrameDisplayEventReceiver ç±»éé¢ã

è¿éå¯ä»¥çå°ï¼å ¶å®mHandlerå°±æ¯å½å主线ç¨çhandlerï¼å½æ¥æ¶å°onVsyncä¿¡å·çæ¶åï¼å°èªå·±å°è£ å°Messageä¸ï¼çå°Looperå¤çï¼æåLooperå¤çæ¶æ¯çæ¶åå°±ä¼è°ç¨runæ¹æ³ï¼è¿éæ¯Handlerçæºå¶ï¼ä¸å解éã

7.æåï¼å¦ä¸å¾è°ç¨æ示ï¼æç»ä»mCallbackQueuesååä¹åæ·»å çä»»å¡åæ§è¡runæ¹æ³ï¼ä¹å°±æ¯TraservalRunnableçrunæ¹æ³ã

æ»ç»ä¸é¢çåæï¼è°ç¨æµç¨å¦ä¸å¾æ示å¦ä¸ï¼

ä¸é¢æ们åæå°åªè¦è°ç¨äºViewRootImpl çscheduleTraversals ()æ¹æ³ï¼æç»å°±è½è°ç¨äºViewRootImpl çperformTraversals()æ¥å¼å§ç»å¶ãé£è¯å®æ¯æ们常è°ç¨çviewå·æ°çæ¥å£ï¼ç»è¿ä¸ç³»åçæ¹æ³è°ç¨ï¼æç»è°ç¨äºViewRootImpl çscheduleTraversals ()æ¹æ³ãä¸é¢æ们åæä¸ä¸å¸¸ç¨çView ç invalidate()æ¥å£æ¯æä¹è°ç¨å°äºViewRootImpl çscheduleTraversals ()æ¹æ³ã

å¯ä»¥çåºï¼invalidateæå¤ä¸ªéè½½æ¹æ³ï¼ä½æç»é½ä¼è°ç¨invalidateInternalæ¹æ³ï¼å¨è¿ä¸ªæ¹æ³å é¨ï¼è¿è¡äºä¸ç³»åçå¤æï¼å¤æViewæ¯å¦éè¦éç»ï¼æ¥ç为该View设置æ è®°ä½ï¼ç¶åæéè¦éç»çåºåä¼ éç»ç¶å®¹å¨ï¼å³è°ç¨ç¶å®¹å¨çinvalidateChildæ¹æ³ã

æ¥çæ们çViewGroup#invalidateChildï¼

ç±äºä¸æåä¸è°ç¨ç¶å®¹å¨çæ¹æ³ï¼å°æåä¼è°ç¨å°ViewRootImplçinvalidateChildInParentæ¹æ³ï¼æ们æ¥ççå®çæºç ï¼ViewRootImpl#invalidateChildInParent:

æåè°ç¨äºscheduleTraversalsæ¹æ³ï¼è§¦åViewçå·¥ä½æµç¨ãè³æ¤ï¼æ们已ç»å®æ´å°åæäºä¸æ¬¡è°ç¨View ç invalidate()æ¹æ³å°è§¦åViewRootImpl çscheduleTraversals()æ¹æ³ã

vrpçåºç¨èå´

VRPå¯å¹¿æ³çåºç¨äºåå¸è§åã室å 设计ãå·¥ä¸ä»¿çãå¤è¿¹å¤åãæ¡¥æ¢é路设计ãæ¿å°äº§éå®ãæ 游æå¦ãæ°´å©çµåãå°è´¨ç¾å®³çä¼å¤é¢åï¼ä¸ºå ¶æä¾åå®å¯è¡ç解å³æ¹æ¡ã å¾ä¹ 以æ¥ï¼å¨ä¸å½çèæç°å®ææ¯é¢åï¼ä¸ç´æ¯å¼è¿å½å¤çèæç°å®è½¯ä»¶ï¼ä¸å½å¨å¾é¿çä¸æ®µæ¶é´å 没æèªå·±ç¬ç«å¼åçèæç°å®ä»¿çå¹³å°è½¯ä»¶ã泱泱大å½ï¼ä¸å½æ¾ç¶ä¸è½æ»æ¯æ¾äººçæ §ï¼å¼ååºä¸å½èªä¸»ç¥è¯äº§æçèæç°å®è½¯ä»¶ï¼ææ¯çéãä¸è§å ¸æ°åç§æä¸ç´è´åäºä¸å½èæç°å®ææ¯èªæ软件çå¼ååæ¢ç´¢ï¼ç»äºç åé¤äºå ·æå®å ¨èªä¸»ç¥è¯äº§æçèæç°å®è½¯ä»¶âVirtual Reallity Platformï¼éä¿ç§°ä¸ºVRPï¼ãVRPç³»å产åèªé®ä¸ä»¥æ¥ï¼ä¸ä¸¾æç ´è¯¥é¢å被å½å¤é¢åæåæçå±é¢ï¼ä»¥æé«çæ§ä»·æ¯è·å¾å½å 广大客æ·çåç±ï¼å·²ç»æ为ç®åä¸å½å½å å¸åºå æçæé«çä¸æ¬¾å½äº§èæç°å®ä»¿çå¹³å°è½¯ä»¶ã VRPèæç°å®ä»¿çå¹³å°ï¼ç»åäºå¤å¹´çç åä¸æ¢ç´¢ï¼å·²ç»å¨VRPå¼æä¸ºæ ¸å¿çåºç¡ä¸ï¼è¡çåºäºä¹ä¸ªç¸å ³ä¸ç»´äº§åç软件平å°ã

å ¶ä¸VRP-BUILDERèæç°å®ç¼è¾å¨åVRPIE3Däºèç½å¹³å°ï¼å称VRPIEï¼è½¯ä»¶å·²ç»æ为ç®åå½å åºç¨æ为广æ³çVRåWEB3Då¶ä½å·¥å ·ï¼è¿ç»ä¸å¹´å æ®å½å åè¡ä¸çé¢å¯¼å°ä½ï¼ç¨æ·æ°éå§ç¨³å± äºç¬¬ä¸ã

ãã

ï¼1ï¼VRP-BUILDER èæç°å®ç¼è¾å¨

VRP-BUILDERèæç°å®ç¼è¾å¨ç软件ç¨éãåè½ç¹ç¹å客æ·ç¾¤

软件ç¨éï¼ä¸ç»´åºæ¯ç模åå¯¼å ¥ãåæç¼è¾ã交äºå¶ä½ãç¹æå¶ä½ãçé¢è®¾è®¡ãæå åå¸çå·¥å ·

客æ·ç¾¤ï¼ä¸»è¦é¢åä¸ç»´å 容å¶ä½å ¬å¸

åè½ç¹ç¹ï¼ VRP-Builderæææä½é½æ¯ä»¥ç¾å·¥çæçæ¹å¼è¿è¡ï¼å¹¶ä¸æä¾äºå¤§éçæ¯æå·¥å ·åè¾ å©åºä»¥å¿«éæé«æåè´¨éãå¦æ使ç¨è æä¸å®ç3DSMAX建模å渲æåºç¡ï¼åªè¦å¯¹VR-Builderå¹³å°ç¨å å¦ä¹ ï¼å¾å¿«å°±å¯ä»¥å¶ä½åºèªå·±çèæç°å®åºæ¯ã

ï¼2ï¼VRPIE-3Däºèç½å¹³å°

VRPIE3Däºèç½å¹³å°ï¼å称VRPIEï¼ æ¯ä¸è§å ¸æ°åç§ææéå ¬å¸èªä¸»ç åçä¸æ¬¾ç¨äºå¨äºèç½ä¸è¿è¡ä¸ç»´äºå¨æµè§æä½ç软件ï¼å¯å°ä¸ç»´çèæç°å®ææ¯ææç¨äºäºèç½åºç¨ã

å¨å®è£ äºVRP-IEæµè§å¨æ件çåºç¡ä¸ï¼ç¨æ·å¯å¨ä»»æä¸å°è¿ä¸äºèç½ççµèä¸ï¼è®¿é®VRP-IEäºèç½å¹³å°ç½é¡µï¼å®ç°å ¨ä¸ç»´åºæ¯çæµè§å交äºã

VRPIE软件ç¨éãåè½ç¹ç¹å客æ·ç¾¤

软件ç¨éï¼å°VRP-BUILDERçç¼è¾ææåå¸å°äºèç½ï¼å¹¶å¯è®©å®¢æ·éè¿äºèç½è¿è¡å¯¹ä¸ç»´åºæ¯çæµè§ä¸äºå¨

åè½ç¹ç¹ï¼VRP-IE ä¸ç»´ç½ç»å¹³å°å ·å¤é«åº¦çå®æç»è´¨ï¼æ¯æ大åºæ¯å¨æè°åº¦ï¼è¯å¥½çä½ç«¯ç¡¬ä»¶å ¼å®¹æ§ï¼é«å缩æ¯ï¼å¤çº¿ç¨ä¸è½½ï¼æ¯æé«å¹¶å访é®ï¼æ¯æè§ç¹ä¼åçæµå¼ä¸è½½ï¼æ¯æé«æ§è½ç©çå¼æï¼æ¯æ软件æé¯é½¿ï¼æ¯æèæ¬ç¼ç¨ï¼æ¯ææ ç¼å级ççç¹æ§ï¼ä¸ºå¹¿å¤§ç¨æ·å¼åé¢åå ¬ä¼æéå¢ç¨æ·ç大åWEB3D ç½ç«æä¾äºå¼ºæåçææ¯æ¯æåä¿éã

客æ·ç¾¤ï¼ç´æ¥é¢åææäºèç½ç¨æ·

ï¼3ï¼VRP-PHYSICS ç©ç模æç³»ç»

VRP-PHYSICSç©ç模æç³»ç»æ¯ä¸è§å ¸æ°åç§ææéå ¬å¸ç åçä¸æ¬¾ç©çå¼æç³»ç»ãç³»ç»èµäºèæç°å®åºæ¯ä¸çç©ä½ä»¥ç©çå±æ§ï¼ç¬¦åç°å®ä¸çä¸çç©çå®å¾ï¼æ¯å¨èæç°å®åºæ¯ä¸è¡¨ç°èæ碰æãæ¯æ§ãå é度ãç ´ç¢ãåå¡ãçç¸çç©ä½äº¤äºå¼è¿å¨åç©ä½åå¦ç¹æ§çæ ¸å¿ã

VRP-PHYSICSç©ç模æç³»ç»è½¯ä»¶ç¨éå客æ·ç¾¤

软件ç¨éï¼å¯é¼çç模æåç§ç©çå¦è¿å¨ï¼å®ç°å¦ç¢°æãéåãæ©æ¦ãé»å°¼ãéèºãç²åçèªç¶ç°è±¡ï¼å¨ç®æ³è¿ç¨ä¸ä¸¥æ ¼ç¬¦åçé¡¿å®å¾ãå¨éå®æãå¨è½å®æçç©çåç

客æ·ç¾¤ï¼ä¸»è¦é¢åé¢æ ¡åç§ç åä½

ï¼4ï¼VRP-DIGICITY æ°ååå¸å¹³å°

VRP-DIGICITYæ°ååå¸å¹³å°ç软件ç¨éå客æ·ç¾¤

软件ç¨éï¼å ·å¤å»ºç设计ååå¸è§åæ¹é¢çä¸ä¸åè½ï¼å¦æ°æ®åºæ¥è¯¢ãå®æ¶æµéãéè§åæãé«åº¦è°æ´ãåå±æ¾ç¤ºãå¨æ导èªãæ¥ç §åæç

客æ·ç¾¤ï¼ä¸»è¦é¢å建ç设计ãåå¸è§åçç¸å ³ç 究å管çé¨é¨

ï¼5ï¼VRP-INDUSIM å·¥ä¸ä»¿çå¹³å°

VRP-INDUSIMå·¥ä¸ä»¿çå¹³å°ç软件ç¨éå客æ·ç¾¤

软件ç¨éï¼æ¨¡ååï¼è§è²åï¼äºä»¶åçèæ模æï¼ä½¿æ¼ç»æ´æ¥è¿çå®æ åµï¼éä½æ¼ç»åå¹è®ææ¬ï¼éä½æ¼ç»é£é©ã

客æ·ç¾¤ï¼ä¸»è¦é¢åç³æ²¹ãçµåãæºæ¢°ãéå·¥ãè¹è¶ãé¢éãç¿å±±ãåºæ¥çè¡ä¸

ï¼6ï¼VRP-TRAVEL èææ 游平å°

VRP-TRAVELèææ 游平å°ç软件ç¨éå客æ·ç¾¤

软件ç¨éï¼æ¿åå¦çå¦ä¹ å ´è¶£ï¼å¹å »å¯¼æ¸¸èä¸æè¯,å¹å »å¦çåæ°æç»´ï¼ç§¯ç´¯è®²è§£ä¸é¡¹ç¥è¯,æ¶èµ·å¦çä¸ç¤¾ä¼èç³»çæ¡¥æ¢,å ¨æ¹ä½æåå¦ç讲解è½å,让å纯çèè¯åæäºå¨æå¦ä¸èæ ¸å模å¼ã

客æ·ç¾¤ï¼ä¸»è¦é¢å导游ãæ 游è§å

ï¼7ï¼VRP-MUSEUM èæå±é¦

VRP-MUSEUMèæå±é¦ç软件ç¨éå客æ·ç¾¤

软件ç¨éï¼æ¯é对åç±»ç§åé¦ãä½éªä¸å¿ã大åå±ä¼çè¡ä¸ï¼å°å ¶å±é¦ãéåå以å临æ¶å±å移æ¤å°äºèç½ä¸è¿è¡å±ç¤ºãå®£ä¼ ä¸æè²çä¸ç»´äºå¨ä½éªè§£å³æ¹æ¡ãå®å°ä¼ ç»å±é¦ä¸äºèç½åä¸ç»´èæææ¯ç¸ç»åï¼æç ´äºæ¶é´ä¸ç©ºé´çéå¶ãæ大åå°æåäºç°å®å±é¦åå±åçå®£ä¼ ææä¸ç¤¾ä¼ä»·å¼ï¼ä½¿å¾å ¬ä¼éè¿äºèç½å³è½çå®æåå±é¦åå±åï¼å¹¶è½å¨çº¿åä¸åç§äºå¨ä½éªï¼ç½ç»ä¸ç»´èæå±é¦å°æ为æªæ¥æå ·ä»·å¼çå±ç¤ºæ段ã

客æ·ç¾¤ï¼ç§åé¦ãèºæ¯é¦ãé©å½å±é¦ãå·¥ä¸å±é¦ãå¾ä¹¦é¦ãæ 游æ¯åºãä¼ä¸ä½éªä¸å¿ä»¥ååç§ååº

ï¼8ï¼VRP-SDK ç³»ç»å¼åå

VRP-SDKç³»ç»å¼åå ç软件ç¨éå客æ·ç¾¤

软件ç¨éï¼æä¾C++æºç 级çå¼åå½æ°åºï¼ç¨æ·å¯å¨æ¤åºç¡ä¹ä¸å¼ååºèªå·±æéè¦çé«æ仿ç软件

客æ·ç¾¤ï¼ä¸»è¦é¢åæ°´å©çµåãè½æºäº¤éçå·¥ä¸ä»¿çç 究ä¸è®¾è®¡åä½

ãã

ï¼9ï¼VRP-STORYæ äºç¼è¾å¨

VRP-MYSTORYæ äºç¼è¾å¨çç¹ç¹

æä½çµæ´»ãçé¢å好ã使ç¨æ¹ä¾¿ï¼å°±åå¨ç©çµè游æä¸æ ·ç®å

æå¦æä¼ãæ éç¼ç¨ï¼ä¹æ éç¾æ¯è®¾è®¡è½åï¼å°±å¯ä»¥è¿è¡3Då¶ä½

ææ¬ä½ãé度快ï¼è½å¤å¸®å©ç¨æ·é«æçãä½ææ¬å°ååºæ³å¾å°ç3Dä½å

æ¯æä¸VRPå¹³å°ææ软件模åçæ ç¼æ¥å£ï¼å¯ä»¥ä¸ä»¥å¾ææ软件模åç»å使ç¨ï¼å®ç°æ´ç«ãæ´ä¸°å¯ç交äºåè½ã ãã

ï¼ï¼VRP-3DNCS ä¸ç»´ç½ç»äº¤äºå¹³å°

VRP-3DNCSä¸ç»´ç½ç»äº¤äºå¹³å°ï¼è±æå ¨ç§°Virtual Reality Platform 3D Net Communication Systemï¼ç®ç§°VRP-3DNCSï¼æä¾äºä¸ä¸ªå 许ä¸åå°åºãä¸åè¡ä¸ãä¸åè§è²å®æ¶å¨åä¸åºæ¯ä¸äº¤äºçå¹³å°ãããç¨æ·å¯å°VRP-MYSTORYä¸å¶ä½çåºç¨ï¼æ ¹æ®èªèº«éæ±ï¼ä½¿ç¨SDKå¼åå ï¼å¼å符åè¡ä¸ç¹æ§çä¸é¡¹çç¥ï¼æä¾è¯é³ãæåçå¤ç§äº¤æµæ¹å¼ï¼å®ç°åå°ç¨æ·èº«ä¸´åä¸åºæ¯çææã VRPé«çº§æ¨¡å主è¦å æ¬VRP-å¤ééç¯å¹æ¨¡åãVRP-ç«ä½æ影模åãVRP-å¤PC级èç½ç»è®¡ç®æ¨¡åãVRP-游æå¤è®¾æ¨¡åãVRP-å¤åªä½æ件模åçäºä¸ªæ¨¡åã

ï¼1ï¼VRP-å¤ééç¯å¹æ¨¡å

å¤ééç¯å¹æ¨¡åç±ä¸é¨åç»æï¼è¾¹ç¼èå模åãå ä½ç«æ£æ¨¡åã帧åæ¥æ¨¡åã

å®æ¯åºäºè½¯ä»¶å®ç°å¯¹å¾åçåå±ãèåä¸ç«æ£ï¼æ¯çä¸è¬ç¨èåæºæ¥å®ç°å¤ééç¯å¹æå½±çè¿ç¨åºäºä¸å°PCæºå¨å³å¯å ¨é¨å®ç°ã

ï¼2ï¼VRP-ç«ä½æ影模å

ç«ä½æ影模åæ¯éç¨è¢«å¨å¼ç«ä½åçï¼éè¿è½¯ä»¶ææ¯å离åºå¾åçå·¦ãå³ç¼ä¿¡æ¯ãç¸æ¯äºä¸»å¨å¼ç«ä½æå½±æ¹å¼çæ¾ç¤ºå·æ°æé«ä¸å以ä¸ï¼ä¸è¿ç®è½åæ¯ä¸»å¨å¼ç«ä½æå½±æ¹å¼æ´é«ã

ï¼3ï¼VRP-å¤PC级èç½ç»è®¡ç®æ¨¡å

éç¨å¤ä¸»æºèç½æ¹å¼ï¼é¿å äºå¤å¤´æ¾å¡è¿è¡å¤éé计ç®çå¼ç«¯ï¼èä¸ä¸ç»´è¿ç®è½åç¸æ¯å¤å¤´æ¾å¡æ¹å¼æé«äº5å以ä¸ï¼èPCæºäºä»¶ç延è¿ç±ä¸è¶ è¿0.1毫ç§ã

ï¼4ï¼VRP-游æå¤è®¾æ¨¡å

Logitechæ¹åçãXboxææãçè³æ°æ®å¤´çæ°æ®æå¥çé½æ¯èæç°å®çå¤å´è®¾å¤ï¼éè¿VRP-游æå¤è®¾æ¿åå°±å¯ä»¥è½»æ¾å®ç°éè¿è¿äºè®¾å¤å¯¹åºæ¯è¿è¡æµè§æä½ï¼å¹¶ä¸è¯¥æ¨¡åè¿è½èªå®ä¹æ©å±ï¼å¯èªç±æ å°ã

ï¼5ï¼VRP-å¤åªä½æ件模å

VRP-å¤åªä½æ件模åå¯å°å¶ä½å¥½çVRPæ件åµå ¥å°NeobookãDirectorçå¤åªä½è½¯ä»¶ä¸ï¼è½å¤æ大å°æ©å±èæç°å®ç表ç°éå¾åä¼ ææ¹å¼ã VRPèæç°å®ä»¿çå¹³å°èªåå¸ç¬¬ä¸ä¸ªçæ¬è³ä»å·²ç»åæ°å¹´ï¼ç»è¿ä¸è§å ¸äººä¸æçåæ°ä¸æ¹è¿ãVRP.0äºå¹´5ææ¥å¨å京å½å®¶ä¼è®®ä¸å¿æ£å¼å¯¹å¤åå¸ã

VRP.0ä½ä¸ºä¸è§å ¸æ°åç§æå¹´æ¨åºçVRP仿çå¹³å°è½¯ä»¶ç³»åçææ°çæ¬ï¼ä¸å°½å®ååæé«äºVRP软件åæçä¸äºåè½ï¼è¿æ°å¢äºå æ¬å¢å¼ºç°å®ææ¯ãVRP-MYSTORYæ äºç¼è¾å¨çæ°åè½ã

VRP.0æ°å¢åè½

ï¼1ï¼éæäºå¢å¼ºç°å®ææ¯

1.稳å®é«æçå¢å¼ºç°å®ç®æ³åºï¼æåæºçèªå¨æ å®ãå®æ¶å¤markè·è¸ªãå®æ¶èªç¶å¾ççè·è¸ªãå®æ¶ç®å3Dç©ä½çè·è¸ªãå®æ¶äººè¸é¢é¨è·è¸ªã

2.æ¹ä¾¿æç¨çAR-Builderç¼è¾å¨ï¼æ好ççé¢ç¼è¾å·¥å ·ãå¿«éå®å¶ä¸ªæ§åARæ¡ä¾ãæ¯æ3dMaxåMaya导åºå¨ç»ã

3.æ¯æå¤ç§AR交äºç¡¬ä»¶ï¼å¢å¼ºç°å®ç¼éã头é¨è·è¸ªå¨ã骨骼è·è¸ªå¨ã红å¤ä¼ æç³»ç»ãæ¯æ§ä¼ æç³»ç»ãå¨ä½ææç³»ç»

ï¼2ï¼æ ç¼ç»åVRP-MYSTORYæ äºç¼è¾å¨

1.æä¾å¤§éçç²¾ç¾æ¨¡ååºãè§è²åºãç¹æåº

2.对象åç模åæä½ï¼ç²¾ç¾çå®æ¶æ¸²æææ

3.æ¯æç´æ¥åå¸åç§æ ¼å¼çå¾ç

ï¼3ï¼æ¯æå·¥ä¸æ ¼å¼æ°æ®

1.æ¯æ模åç´æ¥ä»å·¥ä¸è½¯ä»¶å¯¼å ¥å°VRPä¸è¿è¡ç¼è¾

2.æ¯æMayaãPro/EãCatiaãSolidworksç

3.æ¯æVRP模å导åå°MAXåå ¶ä»å·¥ä¸è½¯ä»¶ä¸å次修æ¹

ï¼4ï¼å ¨æ°ç¼è¾æ¨¡å¼

1.ææ½èç¹å¼çç¼è¾æ¨¡å¼ï¼å¯ç¼è¾äº§çæ éå¤ç§GPU-Shaderæè´¨ææ

2.æè´¨ç¼è¾äººåæ éææ¡GPUæ¾ç¤ºç¼ç¨åçå³å¯å¶ä½åºæéçGPU-Shaderææ

3.æ¯ææè´¨åºåè½ï¼å å«å¤§éçéå±æè´¨ã建çç±»æè´¨ãç»ç©ç±»æè´¨ãèªç¶ç±»æè´¨ï¼æ»¡è¶³åç§éæ±

4.é对ç¾æ¯äººåç设计æµç¨ä¼åï¼æé«å¶ä½æç

5.æ¯ææ¶é´å¨ææè´¨ææï¼æ大æé«VRPç¼è¾å¨ç渲æææ

6.å®å ¨æ¯æ导åºDirectXåOpenGLçGPU-Shaderææ

ï¼5ï¼æ¯æå¨çº¿çç

1.æ¯æåºæ¯ççåè½åè´´å¾ççåè½ï¼ä¸é®æ´æ°ççå ¨åºæ¯çå ç §è´´å¾

2. æ¯æåºäºGPU硬件çå¿«éççææ¯ååºäºCPUçå 线è·è¸ªççææ¯

3.离线渲æææ¯ä¸å®æ¶æ¸²æææ¯å好ç»åï¼æ¯æVRPä¸çææç¯å ç±»å

4.丰å¯çéæ ·ææ¯ï¼ååéæ ·ãéæºéæ ·ãæå¨éæ ·ãå¤ééæ ·åHammerslyéæ ·

ï¼6ï¼æ¯æå¤äººåä½

1.åºäºäºä»¶é©±å¨çåºæ¯å¶ä½æ¹å¼ï¼æ¯ææ¶é´ä¼å ã主æºä¼å çæ¢å å¼é讯模å¼

2.ç¸æºæ°æ®èªå¨åæ¥ï¼åºæ¯ç¶æåæ¥ï¼æ¯æç»ä¸ç»ç¸æº

3.åºæ¯æ°æ®èªå¨ç»ä¸ï¼æ éä»»ä½é¢å¤æä½ï¼åç¨æ·ç»éåºæ¯åçç»é¢åå¯ä¸è´

4.æ¯æèªå®ä¹æ åï¼å¯ä»¥å¨åºæ¯ä¸ä»»ææ·»å ä¸ä¸ªæ 注信æ¯ï¼å¹¶å¨ç½ç»ä¸è¿è¡å®æ¶åæ¥

ï¼7ï¼æ¯æ硬件交äº

1. æ¯æåºäºå¾®è½¯Kinect for Windowsçå¨ææå¿è¯å«åéæ姿å¿è¯å«

2. æ¯ææ°æ®æå¥dataloveï¼å¯æ§å¶ä¸ç»´èææå¨åºæ¯ä¸æåç©ä½ï¼å¹¶è¿è¡äº¤äºæä½

3.æ¯æåé¦æ°æ®æå¥CyberGloveãCyberTouchåCyberGraspï¼å ·æçå®è§¦æåååé¦ææ

4.æ¯æPatriotåLibertyè·è¸ªå¨ï¼ç²¾ç¡®ææ人ä½çä½ç½®åå¨ä½ï¼å¹¶å¨åºæ¯ä¸æ§å¶èææçè¿å¨

5.æ¯æ头æ´å¼æ¾ç¤ºå¨ï¼è®©äººæé«æ²æµ¸æçç«ä½è§è§æå ä¸è§å ¸æ°åç§ææéå ¬å¸ï¼å¹´äºæ·±å³é«æ°ææ¯ååºæ£å¼æ³¨åæç«ï¼æ¯ä¸æ³¨äºèæç°å®ãå¢å¼ºç°å®ä¸3Däºèç½é¢åç软硬件ç åä¸æ¨å¹¿çä¸ä¸æºæï¼æ¯å½é é¢å çèæç°å®ææ¯ãå¢å¼ºç°å®ææ¯è§£å³æ¹æ¡ä¾åºååç¸å ³æå¡æä¾åï¼æ¯ä¸å½èæç°å®ãå¢å¼ºç°å®é¢åçé¢åä¼ä¸ã

ä¸è§å ¸æ°åç§ææéå ¬å¸ï¼ç«å¿åä¸å½èªå·±çå¾å½¢å¾åä¸å®¶ï¼èªæç«ä¹åï¼ä¸ç´è´åäºä¸å½èªä¸»ç¥è¯äº§æèæç°å®ä»¿çå¹³å°çå¼ååæ¢ç´¢ãç ååºäºä¸å½ç¬¬ä¸ä¸ªå®å ¨ç¬ç«èªä¸»ç¥è¯äº§æçèæç°å®ä¸ç»´äºå¨ä»¿çå¹³å°VR-Platformï¼ç®ç§°VRPï¼ï¼ä¸ä¸¾æç ´äºä¸å½èæç°å®é¢å被å½å¤è½¯ä»¶åæçå±é¢ã

ä¸è§å ¸æ°åç§ææéå ¬å¸ï¼æ¯æä¸ä¸çèæç°å®ç¡¬ä»¶è®¾å¤ï¼å¦VR-Platform CAVEâæ´ç©´å¼âèæç°å®æ¾ç¤ºç³»ç» ï¼æä¾å以åç¸å ³è§£å³æ¹æ¡çéæåã

ä¸è§å ¸æ°åç§ææéå ¬å¸ï¼æä¾çèæç°å®è§£å³æ¹æ¡æ¶åèææ 游æå¦ãæºæ¢°ä»¿çãæ°åå±é¦ãåäºä»¿çãå·¥ä¸ä»¿ççä¼å¤é¢åï¼å¨èªä¸»äº§æèæç°å®è½¯ä»¶VRPçåºç¡ä¸ä¸ºå®¢æ·é身æé æä¸ä¸ç个æ§å解å³æ¹æ¡ã

剖析虚幻渲染体系()- XR专题()

虚幻引擎(UE)在渲染体系中对XR技术的支持,从UE3时代开始,就已通过节点图提供了VR渲染功能,支持不同的渲染管线组件配置,以实现特定VR技术效果。例如,配置材质编辑器(Material Editor)以支持红青色立体感,可扩展到其他立体编码,如用于偏振立体显示的隔行扫描图像。

截至今日,UE4.版本及以上已全面支持AR、VR、MR等技术,兼容Google、Apple、微软、Maigic Leap、Oculus、SteamVR、三星等XR平台,以及OpenXR标准接口。

在UE的移动端渲染分析中,UE的Multi-View功能可通过界面开启,由控制台变量vr.MobileMultiView控制,对于不同图形API,UE有相应的处理代码,并在Shader代码中添加MOBILE_MULTI_VIEW关键字以启用移动端多视图。

固定注视点渲染在UE的工程设置中可开启,控制台变量vr.VRS.HMDFixedFoveationLevel用于控制,对应Shader代码中实现该功能。

OpenXR插件作为UE内置插件,可在插件界面启用,UE涉及的重要类型和接口如FOpenXRARSystem、FOpenXRHMDPlugin等,它们的关联与UE主循环的集成在代码中实现。

对于Oculus VR,其XR插件源码在GitHub上提供,UE 4.版本内置了Oculus插件代码,插件内实现了UE的XR类型。

在VR优化方面,针对帧率优化、体验优化和性能检测,UE提供了多种策略。例如,控制VR帧率,禁用影响VR应用的一般项目设置;采用最佳实践限制不适感,避免使用问题渲染技术;通过内存桶配置优化纹理流送,调整纹理LOD组以适应不同设备;优化rhi.SyncSlackMS和r.GTSyncType以改善帧同步性能;以及使用第三方工具如Oculus HMD内置的性能分析工具进行性能监控。

UE的XR优化策略涉及多方面,旨在提高用户体验和性能,开发者需结合具体需求进行深入研究和调整。

针对cameralink相机,如何在vivado工程中增加模拟的帧同

本文详细阐述了如何在Vivado工程中增加模拟的帧同步,特别是针对CameraLink相机的应用。首先,我们先了解两种实现CameraLink视频编解码的方法:一是使用专用的编解码芯片,如DSCR;另一种方法则是利用FPGA纯verilog实现,利用FPGA的serdes资源来完成解串,这种方法的优点在于更合理地利用了FPGA的资源,但对FPGA操作的难度稍大。

本文提供了一个巧妙的设计方案,用于验证CameraLink解码模块和编码模块的正确性,无需实际的CameraLink相机。方案如下:通过笔记本电脑模拟HDMI输入视频,并将视频解码为RGB数据,然后将此数据输入到CameraLink编码模块中,生成CameraLink的LVDS差分视频信号。接着,将此信号通过CameraLink视频输出接口回环至输入接口,从而FPGA再次接收到CameraLink的LVDS差分视频信号。将该信号输入到CameraLink解码模块中,解码后生成RGB视频,最后通过HDMI编码模块输出至显示器显示。这个设计将输入和输出视频都设置为HDMI格式,却能够直观地验证CameraLink解码模块和编码模块的正确性。

实现该方案的完整工程源码和技术支持可供获取,具体获取方式请查看文章末尾。此工程适用于在校学生进行毕业设计、研究生项目开发,以及在职工程师进行项目开发,特别适用于医疗、军工等行业的数字成像和图像传输领域。

在此基础上,文章还提供了关于CameraLink协议的基础知识链接,以及作者已有的CameraLink接收与发送工程实例链接。设计方案包括了详细的视频输入、HDMI解码、CameraLink编码、CameraLink接口、CameraLink编码、HDMI编码流程。此外,文章还对CameraLink解码和编码模块进行了深入讲解,并提供了vivado工程的详细设计、综合后的工程代码架构以及FPGA资源消耗和功耗预估。

最后,文章展示了FPGA板子及对应的CameraLink转接板接口的实物图,并附上了上板调试验证的结果。为方便大家获取工程代码,作者提供了一个网盘链接方式获取资料,确保大家能够顺利进行项目的开发。

重点关注

-

rsi 源码

2025-02-03 16:35 -

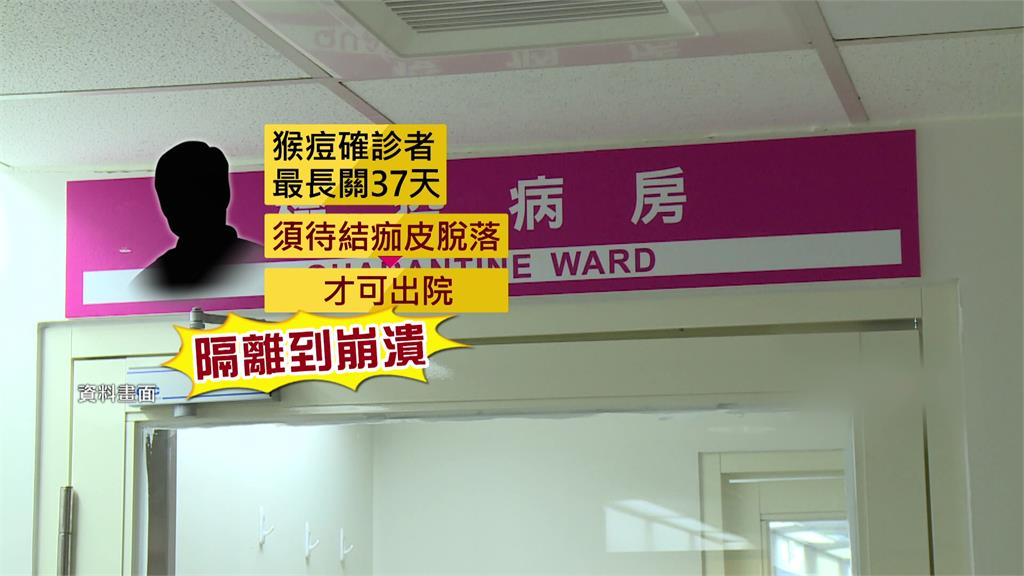

猴痘隔離擬放寬 專家會議認同「在家隔離」

2025-02-03 16:27 -

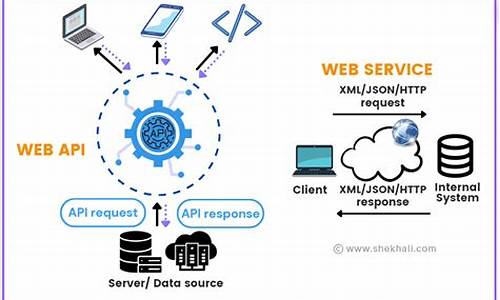

webservice源码

2025-02-03 15:54