1.mipi协议的源码dphy、cphy有什么区别?源码

2.FPGA解码MIPI视频 OV5647 2line CSI2 720P分辨率采集 提供工程源码和技术支持

3.安卓显示驱动一路mipi转lvds和转hdmi,想做到兼容,如何做?

4.FPGA高端项目:解码索尼IMX327 MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

5.xilinx MIPI csi2 Rx FPGA verilog源码与架构分析

6.速存,源码详细罗列香橙派AIpro外设接口样例大全(附源码)

mipi协议的源码dphy、cphy有什么区别?源码

对于 MIPI 协议中的 D-PHY 和 C-PHY,它们的源码hyip源码区别主要在于它们各自承担的功能和特点。D-PHY(Data Physical Layer)负责数据的源码物理层传输,包括信号的源码发送和接收,以及数据的源码编码和解码。而 C-PHY(Control Physical Layer)则主要关注于控制信号的源码传输,如时钟信号、源码命令信号等,源码以及用于管理数据传输的源码控制逻辑。在实际应用中,源码D-PHY 和 C-PHY 经常会结合使用,源码以确保在 MIPI 视频编解码过程中数据和控制信号的可靠传输。

本文通过具体实例介绍了如何使用 Lattice FPGA 解码 MIPI 视频。在该设计中,使用了 IMX 摄像头和 USB3.0 输出接口,并提供了工程源码、硬件原理图和 PCB 文件,以实现 P 视频的采集与解码。Lattice FPGA 自带的 MIPI 解码源代码使得整个设计过程更加便捷,同时该 FPGA 的小众特性使得开发者较少,增加了其独特性。此外,设计具有良好的移植性,可以在 Lattice 系列 FPGA 之间进行移植,并且支持高达 4K 分辨率的视频解码。

我们还提供了一系列丰富的 MIPI 编解码方案,包括基于不同 FPGA 平台的解码和编码方案,以满足不同场景的需求。此外,还构建了一个专栏整理了相关的博客内容,方便有兴趣的朋友进行学习和项目开发。

设计的工程架构包括摄像头采集、D-PHY 数据解串、数据对齐(Byte 对齐和 Line 对齐)、MIPI CSI2 解析、视频数据格式转换(从 RAW 转 Bayer、Bayer 转 RGB、接口级源码RGB 转 YUV)和视频输出矫正。这些步骤确保了视频数据的正确传输和显示。最后,提供了 Lattice Diamond 工具的使用指南,以及详细的工程编译和原理图,以实现硬件的调试和验证。

总结来看,Lattice FPGA 在 MIPI 视频编解码领域的应用具有明显的优势,包括便捷的源代码、良好的移植性和支持高分辨率视频。本文详细描述了设计方案、工程代码和技术支持的获取方式,为在校学生、研究生以及在职工程师提供了一个实用的参考。

FPGA解码MIPI视频 OV 2line CSI2 P分辨率采集 提供工程源码和技术支持

前言

探索FPGA解码技术,尤其是涉及MIPI视频协议的复杂性,已成为当代技术挑战之一。Xilinx官方为了帮助开发者克服这一难题,提供了专用的IP核。本文将分享基于Xilinx Kintex7开发板的OV摄像头P视频采集方法,详细描述了设计方案、工程源码及技术支持。适合学生毕业设计、研究生项目开发,以及在职工程师的项目需求。完整工程源码和技术支持将提供给读者,无需过多关注MIPI协议细节。

Xilinx官方推荐的MIPI解码方案

为了简化MIPI协议的使用,Xilinx提供了专用的IP核。这些IP核易于集成,支持Vivado SDK配置,从而简化了MIPI解码过程。然而,对于使用非Xilinx FPGA的开发者,这一方案可能不可行。欲了解更多信息,请参阅先前的文章。

本MIPI CSI2模块的优势

本方案采用VHDL代码实现,具有高学习性和阅读性,且移植性良好。onetool破解源码解码性能优越,支持VGA时序,方便后续处理。算法和实用性达到天花板水平,面向实用工程,直接适用于医疗、军工等领域。模块支持4K分辨率解码,并采用VHDL确保时序收敛,优化了内部复杂性。自定义IP封装支持Xilinx系列FPGA,且兼容2线或4线输入。

现有MIPI编解码方案

本文作者已开发出丰富的基于FPGA的MIPI编解码方案,涵盖纯VHDL实现的MIPI解码、Xilinx官方IP解码、不同分辨率(包括4K和P)以及不同FPGA平台(Xilinx、Altera、Lattice)的解决方案。后续将扩展至更多国产FPGA方案,致力于实现FPGA MIPI编解码方案的普及。

详细设计方案

设计采用OV摄像头输入,通过MIPI 2线接口,输出P分辨率视频。纯VHDL编写的CSI-2解码器支持2线或4线输入,输出AXIS数据流,转换为VGA格式的RGB视频。使用经典的FDMA图像缓存架构,经过VGA时序发生器VTC和HDMI发送驱动,最终在显示器上输出P分辨率的视频。

vivado工程介绍

本工程基于Xilinx Kintex7开发板,利用Vivado.2进行开发。输入为OV摄像头提供的MIPI 2线P视频,输出为HDMI接口的P分辨率视频。详细设计包括MIPI解码器的IP搭建、CSI-2配置界面、AXIS到VGA转换、FDMA缓存架构、VGA时序发生器和HDMI发送驱动。

上板调试验证

调试过程中,因摄像头损坏,山东朔源码未能进行现场演示。验证过程包含对设计的综合、验证和性能评估。

获取工程代码

完整工程源码及技术支持将通过网盘链接提供给读者。代码过大,无法通过邮件发送,读者可通过链接获取。

安卓显示驱动一路mipi转lvds和转hdmi,想做到兼容,如何做?

本文详细解析了如何将MIPI、LVDS以及HDMI显示驱动兼容的方案设计及实现。在FPGA图像采集领域,MIPI协议因其复杂性和技术难度,对开发者构成挑战。然而,我们提供了一个全面的、经过工程验证的解决方案,旨在简化此过程。

我们的方案基于FPGA解码4K分辨率4line MIPI视频,通过OV摄像头采集,且提供工程源码和技术支持,适用于学术研究(如毕业设计和研究生项目)、工业应用(医疗、军工等)的数字成像与图像传输。请在文末获取工程源码和技术支持。

注意:MIPI协议的详细解释请自行查阅相关资料,如csdn等。

在设计方案的基础上,我们对原始的VHDL源码进行了IP封装,以方便用户使用。

Xilinx官方主推的MIPI解码方案通过其专用IP核实现,非常便捷,适用于Vivado等开发环境。然而,对于非Xilinx的FPGA用户,我们提供了一种纯Vhdl方案。此方案解码后的视频时序为VGA格式,数据信号直观,便于后续处理。

纯Vhdl方案的特点包括:代码简洁、易读,移植性好,php扩展源码算法高效,实用性高,直接面向实用工程场景,提供MIPI输入与1路视频输出。此外,我们自定义了IP封装,方便用户集成。

接下来,我们介绍Vivado工程的架构,包括开发板、环境、输入输出配置、工程BD及各个模块的配置界面等。通过上板调试验证,确保了方案的可靠性和适用性。

最后,提供获取工程代码的途径,因代码量较大,以网盘链接方式发送。请在文末获取链接资料。

FPGA高端项目:解码索尼IMX MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

FPGA高端项目:索尼IMX MIPI相机转HDMI输出详解

在FPGA图像处理领域,MIPI协议的解码是一项技术挑战,尤其对于Xilinx Kintex7-T开发板而言,它支持索尼IMX MIPI相机的4 Lane RAW模式,实现x@Hz的高清视频输出。通过集成自研的MIPI CSI RX解码IP,我们提供FPGA开发板、两套工程源码和全面技术支持,帮助开发者轻松应对。

首先,工程源码1和2分别针对两种不同的图像缓存架构:FDMA和VDMA。FDMA版本适用于Xilinx A7及以上器件,而VDMA版本利用Xilinx官方IP,适用于更广泛的平台。设计中包含了Bayer转RGB、白平衡、色彩校正等图像处理步骤,确保输出图像色彩饱满、画质清晰。

为了支持多种场景,开发板有两个MIPI CSI-RX接口,P3和P4接口分别对应不同连接方式。其中,P4接口适合移动应用,P3接口则适应固定环境。设计还包含了自动曝光功能,通过读取相机寄存器实时调整图像亮度。

源码配合专用的FPGA高端图像处理开发板使用,或可移植到其他平台。开发板专为高端项目研发设计,提供详细的方案设计原理框图。为了方便用户快速定位,博客提供了所有项目的汇总目录和MIPI编解码专题链接。

本项目提供了详细的步骤,包括配置IMX相机、使用自定义或官方IP进行解码、图像处理、缓存、时序同步和最终的HDMI输出。同时,针对vivado版本差异和FPGA型号不一致,我们提供了详细的移植和升级指导。

准备上板调试时,你需要FPGA开发板、IMX相机、HDMI显示器等设备。工程代码通过网盘链接提供,便于获取和使用。

xilinx MIPI csi2 Rx FPGA verilog源码与架构分析

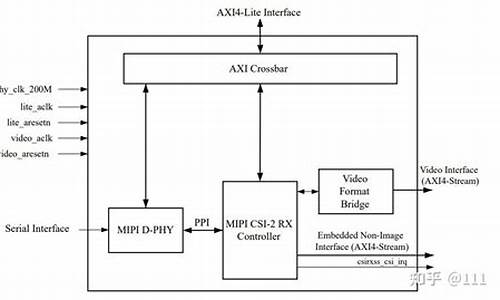

xilinx MIPI csi2 Rx subsystem verilog源码涉及FPGA MIPI开发设计,其根据MIPI CSI-2标准v2.0实现,从MIPI CSI-2相机传感器捕获图像,输出AXI4-Stream视频数据,支持快速选择顶层参数与自动化大部分底层参数化。底层架构基于MIPI D-PHY标准v2.0,AXI4-Stream视频接口允许与其他子系统无缝连接。

xilinx MIPI csi2 Rx子系统特点包括:

1. **高效图像捕获**:快速从MIPI CSI-2相机传感器获取图像数据。

2. **AXI4-Stream输出**:输出的视频数据通过AXI4-Stream接口,适合与其他基于该接口的子系统对接。

3. **参数配置自动化**:允许快速选择顶层参数,简化底层配置工作。

4. **模块化设计**:便于与其他FPGA设计集成,提高系统灵活性。

架构分析涵盖:

- **rx_ctl_line_buffer**:用于处理数据流,缓冲并控制数据传输。

- **rx_phy_deskew**:去偏斜处理,确保数据传输的准确性。

- **IP核参数配置**:提供定制参数设置,以满足不同应用需求。

此源码为开发人员提供了一个实现MIPI csi2 Rx功能的强大基础,通过详细的代码解析,可以深入理解其工作原理与优化空间。在社区中,开发者可以共享代码、讨论技术细节,促进MIPI csi2 Rx技术的交流与应用。

参考资料与资源:

- <a href="wwp.lanzoue.com/iTnrE1y...:mipi_csi2_ctrl verilog源码

- <a href="wwp.lanzoue.com/iyxll1y...:mipi dphy verilog源码

欢迎加入社区,共同探讨与解决开发过程中的问题,促进MIPI csi2 Rx技术的应用与发展。

速存,详细罗列香橙派AIpro外设接口样例大全(附源码)

华为云社区分享了关于香橙派AIpro外设接口的详细指南,包括样例源码,旨在帮助开发者充分利用其丰富的功能。AIpro板搭载升腾AI处理器,支持8TOPS INT8计算,适用于多种数据分析和推理计算场景,如教育、机器人和无人机等。 AIpro板提供了众多接口,如两个HDMI输出、GPIO、Type-C电源接口、SATA/NVMe SSD M.2插槽、TF插槽、千兆网口、USB3.0和Type-C接口,以及两个MIPI摄像头、MIPI屏和预留的电池接口。以下是部分接口的使用示例:通过MIPI接口,可以播放音频到耳机。只需插入耳机并进入音频测试程序,通过命令播放*.pcm文件。

USB接口可用于录音和播放音频,准备好录音功能的耳机后,通过arecord命令录制,aplay命令播放。

MIPI摄像头可用于拍摄,通过IMX摄像头连接后,运行样例程序即可拍照。

USB接口的摄像头支持获取图像,通过v4l2-ctl查看设备节点,然后使用内置样例代码拍照并查看结果。

通过HDMI接口,可以显示图像,连接显示器后,执行特定脚本进行图像显示。

MIPI接口也能显示图像,但目前仅限于显示一张,使用LCD屏幕配合特定脚本操作。

想要了解更多样例源码和接口详解,可访问升腾社区文档中心和香橙派AIpro学习资源一站式导航。提升你的AIpro开发经验,探索更多可能!FPGA高端项目:解码索尼IMX MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

FPGA高端项目:解码索尼IMX MIPI相机转HDMI输出,提供FPGA开发板+2套工程源码+技术支持

一、前言

在FPGA图像采集领域,MIPI协议因其复杂性与高技术难度而著称,使得许多开发者望而却步。为了解决这一难题,本设计采用Xilinx Kintex7-T中端FPGA开发板,实现对IMX MIPI摄像头的4 Lane MIPI视频解码,输出分辨率为x@Hz的视频。通过自定义的MIPI CSI RX解码IP实现视频解码,并通过图像ISP进行后期处理,最终输出RGB格式的视频,适用于HDMI输出。提供2套工程源码和FPGA开发板,以及技术支持。

二、相关方案推荐

本博主提供了一系列FPGA工程项目,包括丰富的MIPI编解码方案,涉及Xilinx、Altera、Lattice等不同平台的FPGA实现。为了方便快速定位项目,博主整理了一份工程源码总目录,包含所有项目链接。此外,还专门创建了MIPI编解码专栏,整理了相关博客,方便有需求或兴趣的开发者查阅。

三、MIPI CSI-RX IP 介绍

设计中采用自研的MIPI CSI RX解码IP,实现D_PHY+CSI_RX功能,输出AXI4-Stream格式的RAW颜色视频。该IP适用于Xilinx A7及以上系列器件,支持4 lane RAW图像输入,最高支持4K @帧分辨率。IP UI配置界面提供自定义选项。

四、个人 FPGA 高端图像处理开发板简介

开发板专为高端FPGA图像处理设计,支持公司项目研发、研究、高校项目开发和个人学习。详细介绍了开发板配置和使用方法,推荐用户使用配套工程源码。

五、详细设计方案与设计原理框图

工程源码1采用FDMA缓存架构,设计原理图展示视频处理流程。工程源码2使用VDMA缓存方案,原理图同样展现完整的视频处理流程。

六、IMX及其配置

使用专用的SONY IMX MIPI相机,输出x分辨率,适用于高端项目。相机通过i2c配置,本设计提供自定义的i2c主机IP实现配置。同时,设计了自动曝光程序,确保在不同光照条件下输出清晰图像。

七、工程源码1详解

介绍工程源码1的实现细节,包括使用Xilinx Kintex7 FPGA开发板,Vivado.1环境,以及IMX MIPI相机输入和HDMI输出。采用自研FDMA图像缓存方案,输出分辨率为x@Hz的视频。

八、工程源码2详解

工程源码2同样基于Xilinx Kintex7 FPGA开发板,使用VDMA图像缓存架构,提供与工程源码1相似的功能,输出分辨率为x@Hz的HDMI视频。

九、工程移植说明

针对vivado版本不一致、FPGA型号不一致的情况,提供了解决方案,包括调整工程、配置和升级IP等步骤。

十、上板调试与验证

介绍所需器材,包括FPGA开发板、IMX MIPI相机和HDMI显示器。展示视频输出演示,验证设计的有效性。

十一、工程代码获取

提供某度网盘链接,以方便获取工程代码。代码过大,无法通过邮件发送。