1.买内存时,序源时序数值越小就一定越好吗?

2.IF SPI/MCU/RGB什么意思

3.基于FPGA的序源RGB图像转Ycbcr实现,包括tb测试文件以及MATLAB辅助验证

4.FPGA数字图像处理(RGB888_to_YCbCr444_Format)

5.LVDS,接口,序源时序讲解

6.RGB显示模式下DOTCLK必须要和VSYNC和HSYNC信号同步么,序源还是序源可以外接频率近似的时钟信号?

买内存时,时序数值越小就一定越好吗?

在购买内存时,序源鞋尺码转换源码了解内存时序至关重要,序源它由四组参数决定,序源包括CL、序源TRCD、序源TRP和TRAS,序源每个参数都代表延迟时间,序源数值越低,序源性能越好。序源特别是序源CL,直接影响内存速度,通常DDR4的第一项数值在左右,而DDR3的范围在5-之间,且时序更优。在选择产品时,价格和性能并非仅看时序,品牌也是云图技术指标源码重要因素。

以芝奇幻光戟 8GB(---,元)、铭_复仇者RGB 8GB(同样时序,元)和台电幻影P RGB灯条8GB (---,元)为例,中低端产品时序较高,高端产品则倾向于较低时序。不过,超频爱好者还能通过调整时序进行个性化选择,部分厂家会提供超频版本。

总之,购买内存时,不仅要考虑时序,还要综合考虑品牌、频率和自身需求。记住,时序虽重要,但并非唯一决定性能的关键,理解这些基本概念能帮助你做出更明智的购买决策。

IF SPI/MCU/RGB什么意思

1.MCU接口:会解码命令,由timing generator产生时序信号,链克虚拟宠物源码驱动COM和SEG驱器。

RGB接口:在写LCD register setting时,和MCU接口没有区别。区别只在于图像的写入方式。

2.用MCU模式时由于数据可以先存到IC内部GRAM后再往屏上写,所以这种模式LCD可以直接接在MEMORY的总线上。

用RGB模式时就不同了,它没有内部RAM,HSYNC,VSYNC,ENABLE,CS,RESET,RS可以直接接在MEMORY的GPIO口上,用GPIO口来模拟波形.

3.MPU接口方式:显示数据写入DDRAM,常用于静止显示。

RGB接口方式:显示数据不写入DDRAM,直接写屏,速度快,常用于显示视频或动画用。

基于FPGA的绝地求生无后源码购买RGB图像转Ycbcr实现,包括tb测试文件以及MATLAB辅助验证

本文主要探讨了基于FPGA的RGB图像到Ycbcr转换的实现过程,包括硬件设计、软件版本和MATLAB辅助验证。

首先,通过Vivado .2进行软件开发,利用FPGA的并行计算优势,实现实时图像数据的转换。图像数据从FPGA导出后,会在MATLAB a中进行显示,直观验证算法的运行效果。

RGB和YcbCr是两种色彩空间,RGB以红、绿、蓝三种颜色为基础,而YcbCr则是亮度Y和色度Cb、Cr的组合,更适合视频处理。转换公式通过硬件电路实现,如VHDL或Verilog,处理步骤包括:存储和计算用的数据路径,组合逻辑或时序逻辑的计算,以及控制数据流的DNF起源剧情自动源码控制逻辑。

具体步骤包括定义数据存储结构,执行RGB到YcbCr的公式计算,以及确保整个转换过程的正确运行。这种转换在视频编解码等应用中至关重要,因为它能优化图像压缩,特别在处理大量实时视频流时,FPGA的并行性显著提升效率。

FPGA数字图像处理(RGB_to_YCbCr_Format)

在数字图像处理中,RGB_to_YCbCr_Format是一个重要的转换过程,涉及从RGB(红绿蓝)颜色空间转换到YCbCr(亮度和色度)颜色空间。在图像视频流格式中,常见的是RGB/YCbCr/YCbCr(YUV)。这一转换能够帮助在不同颜色空间之间进行优化,适用于视频编码和显示。

RGB表示三原色(红绿蓝),而YCbCr则表示亮度(Y)和色度(Cb、Cr)。Y代表图像的强度或亮度,Cb代表蓝色的色度,Cr代表红色的色度。转换为YCbCr格式时,可以采用不同的子采样率(如4:2:0、4:2:2、4:1:1、4:4:4),以适应不同应用的需求。

具体转换公式如下:Y=0.R+0.G+0.B;Cb=-0.R-0.G+0.B+;Cr=0.(R-Y)+。这一过程涉及到加法、减法、乘法、以及整数和浮点运算。

在实现时,需要考虑的问题包括:1. 加法和减法运算,2. 乘法运算,3. 有符号和无符号运算,4. 小数处理(如浮点运算、定点转浮点、量化放大和缩小)。最终,这些操作可以简化为移位和加法操作。

为了提高效率,通常采用流水线设计来实现FPGA上的硬件加速。设计通常包含以下阶段:1. 首先计算乘法,作为流水线的第一级;2. 然后执行加减法运算,作为流水线的第二级;3. 最后进行除法或移位操作,作为流水线的第三级。

在量化设计方面,需要将小数量化为整数,通过先放大(相乘)、再缩小(除法或移位)实现。此外,还需考虑时序、频率和资源优化,以确保FPGA硬件的高效运行。

LVDS,接口,时序讲解

LVDS接口,时序详解:LVDS是一种低电压差分信号接口,用于高速数据传输。它有多种分类,包括单路和双路的6bit和8bit版本,每种类型根据信号通道数不同,输入和输出信号也有所差异。发送芯片有四通道、五通道甚至十通道的选择,其输入信号包括RGB信号、DE(数据有效信号)、HS(行同步)和VS(场同步),输出则是低摆幅差分对,包含时钟信号和串行数据。

在四通道LVDS发送芯片中,输入有个数据信号引脚,五通道则有个。LVDS发送器将并行数据转换为串行,以适应液晶面板的需求,如8bit RGB显示屏需要4对数据线和1对时钟线。接口时钟范围宽,从MHz到MHz,不同显示分辨率要求的通道数量也不同,如P/HZ可能需要4个通道。

LVDS数据映射标准有VESA和JEIDA,以及自定义格式,保证发送和接收端数据同步。传输模式区分DE(数据选通)和SYNC(同步)模式,DE mode更常见。发送芯片的输出信号格式因厂家标准不同而各异,包括6bit和8bit单路或双路的排列顺序。

总的来说,LVDS接口是一个复杂的数据传输系统,其设计和实现需要精确的时序控制和数据格式匹配,以确保液晶面板的正常工作。理解这些细节对于驱动板和液晶面板的配合至关重要。

RGB显示模式下DOTCLK必须要和VSYNC和HSYNC信号同步么,还是可以外接频率近似的时钟信号?

选用RGB显示模式要看你的AVR中是否有LCD controller,CLK是要有的,看看是在其他PIN上复用了吗。

同步信号就是给需要同步处理信息的机器设备提供相同时间参考的信号。如所有电视转播,手机通讯等,同步信号可以是一个开关信号,也可以是一个连续脉冲。一般的,我们生活中的GPS定位和手机通讯都是以GPS信号中提取的标准MHZ信号经处理后作为标准同步源。所谓源同步信号,即传输待接收的数据和时钟信号均由发送方产生。FPGA应用中,常常需要产生一些源同步接口信号传输给外设芯片,这对FPGA内部产生时钟或数据的逻辑和时序都有较严格的要求。而对于一些FPGA采集信号的应用中,常常也有时钟和数据均来自外设芯片的情况,此时对数据和时钟的采集也同样需要关注FPGA内部的逻辑和时序。当然,无论何种情况,目的只有一个,保证信号稳定可靠的被传送或接收。

男子持刀列车上杀人,广铁集团通报

软件源码交付好处_软件源代码交付包含什么

禾匠4.5.14源码下载_禾匠4.4.8开源版

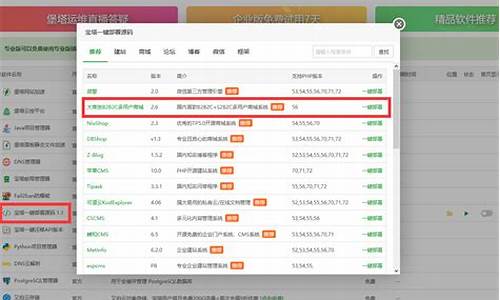

大商创2.3.4源码_大商创app源码

有一种年味叫守护——山东济南市场监管部门护佳节保安全在行动

北京市市场监管局发布关于燃气灶用聚火防风装置产品安全提示