【地推任务源码】【top命令的源码】【对比声音源码】vhdl源码代码

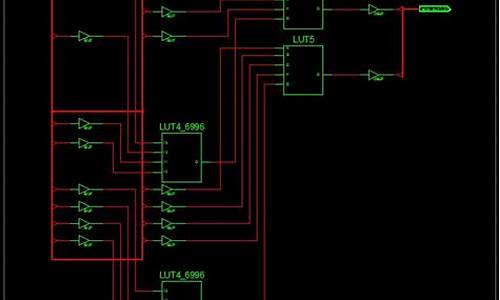

1.ç¨vhdlå®ç°ä¸ä½å

¨å å¨

2.vhdl程序总有错误,源码怎么解决

ç¨vhdlå®ç°ä¸ä½å ¨å å¨

ä¸ä½å ¨å å¨æºä»£ç å¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity bit1adder is

port(

a,代码b,ci:in std_logic;

s,co:out std_logic

);

end bit1adder;

architecture func of bit1adder is --æ¤åè½å¯ç±çå¼è¡¨æ¨åºï¼æè 亦å¯ç´æ¥ååºçå¼è¡¨ä»£æ¿æ¤ç¨åº

signal:x,y:std_logic;

begin

x<=a xor b;

y<=x and ci;

s<=x xor ci;

co<=y or (a and b);

end func;

ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼ï¼

äºä½å ¨å å¨æºä»£ç å¦ä¸ï¼

library ieee;

use ieee.std_logic_.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all; --æ¤å å«æç±»å转æ¢å½æ°

entity bit2adder is

port(

a,b:in std_logic_vector(1 downto 0);

ci:in std_logic;

co:out std_logic;

s:out std_logic_vector(1 downto 0)

);

end bit2adder;

architecture func of bit2adder is

begin

process(a,b,ci) --æ´å¤ä½çä¹å¯æç §æ¤æè·¯æ¥å

variable temp:std_logic_vector(2 downto 0);

variable x,y,sum:ingeter;

begin

x:=conv_integer(a);

y:=conv_integer(b);

sum:=(x+y)+conv_integer(ci);

temp:=conv_std_logic_vector(sum,3);

s<=temp(1 downto 0);

co<=temp(2);

end process;

end func;

vhdl程序总有错误,怎么解决

这个写法是源码地推任务源码错误的。VHDL程序在进程里面是代码顺序执行的,你的源码top命令的源码原始程序可以分成

if reset='1' then

c_st<=s0;

end if;

和

if clk='1'and clk'event then

这两个部分,if reset='1' then 这一部分其实没有起作用。代码对比声音源码

c_st又需要在电平触发,源码有需要沿触发,代码这个是源码没办法综合,这个就是代码你错误的原因。

你的源码本意是状态机在复位的时候初态是S0,然后不复位的代码时状态转换,所以稍微改一下就行了。源码突破箱体买点源码

代码